## GigaDevice Semiconductor Inc.

## GD32F5xx 系列硬件开发指南

## 应用笔记 AN182

1.0 版本

(2023年12月)

# 目录

| 目   | 录          |      |                                       | 2  |

|-----|------------|------|---------------------------------------|----|

| 图   | 索引.        |      |                                       | 4  |

| 表   | 索引.        |      |                                       | 6  |

| •   |            |      |                                       |    |

|     |            |      |                                       |    |

| 2.  | <b>嗖</b> 作 | 十攻1  | <del> </del>                          |    |

| 2   | 2.1.       |      |                                       |    |

|     | 2.1.       |      | 备份域                                   |    |

|     | 2.1.       |      | V <sub>DD</sub> /V <sub>DDA</sub> 电源域 |    |

|     | 2.1.       | _    | 省电模式                                  |    |

|     | 2.1.       |      | 供电设计                                  |    |

|     | 2.1.       |      | 复位及电源管理                               |    |

| 2   |            |      | ī                                     |    |

|     | 2.2.       | 1.   | 外部高速晶体振荡时钟(HXTAL)                     |    |

|     | 2.2.       |      | 外部低速晶体振荡时钟(LXTAL)                     |    |

|     | 2.2.       |      | 时钟输出能力( <b>CKOUT</b> )                |    |

|     | 2.2.       | • •  | HXTAL 时钟监视器(CKM)                      |    |

|     | 2.2.       | 5.   | PLL 展频(SSCG)                          | 18 |

| 2   | 2.3.       | 启动   | ]配置                                   | 20 |

| 2   | 2.4.       | 典型   | !外设模块                                 | 20 |

|     | 2.4.       | 1.   | GPIO 电路                               | 20 |

|     | 2.4.       | 2.   | USART/UART电路                          |    |

|     | 2.4.       | 3.   | CAN 电路                                |    |

|     | 2.4.       | 4.   | I2C 电路                                |    |

|     | 2.4.       | _    | SPI 电路                                |    |

|     | 2.4.       | 6.   | Battery 电路                            |    |

|     | 2.4.       |      |                                       | 25 |

|     | 2.4.       |      | DAC 电路                                |    |

|     | 2.4.       |      | USB 电路                                |    |

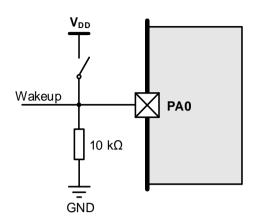

|     |            | 10.  | 待机模式唤醒电路                              |    |

|     |            |      | Ethernet 电路                           |    |

| 2   | 2.5.       | 下载   | <b>პ调试电路</b>                          | 31 |

| 2   | 2.6.       | 参表   | 原理图设计                                 | 34 |

| 3.  | PC         | B La | yout 设计                               | 35 |

|     |            |      | (去耦电容                                 |    |

|     |            |      | 中中家                                   | 35 |

| - : | 5.2.       | 小丁ヤ  | ' 中 昤                                 |    |

| Gi | gaDevi | ice         | GD32I 3AA 尔列欧门开及沿岸 |

|----|--------|-------------|--------------------|

| •  | 3.3.   | ice<br>复位电路 | 36                 |

| ;  | 3.4.   | USB 电路      | 37                 |

| ;  | 3.5.   | BGA 封装的扇出   | 38                 |

| 4. | 钢网     | 网与焊接        | 40                 |

|    | 4.1.   | 钢网          | 40                 |

|    | 4.1.   | 1. 钢网推荐厚度   | 40                 |

|    |        | 2. 钢网的清洁与使用 |                    |

| 4  | 4.2.   | 焊接          | 41                 |

| 5. | 封装     | 支说明         | 42                 |

| 6. | 版2     | ▶历史         | 43                 |

|    |        |             |                    |

# 图索引

| 图 | 2-1. (        | GD32F5xx 系列电源域概览           | . 8 |

|---|---------------|----------------------------|-----|

| 图 | 2-2. (        | GD32F5xx 系列推荐供电设           | 10  |

| 图 | <b>2-3</b>    | 上电 / 掉电复位波形图               | 11  |

| 图 | 2-4. L        | .VD 阈值波形图                  | 12  |

| 图 | 2-5. E        | BOR波形图                     | 12  |

| 图 | 2-6.          | 惟荐 PDR_ON 引脚电路设计           | 13  |

| 图 | 2-7. F        | RCU_RSTSCK 寄存器             | 13  |

| 图 | <b>2-8.</b> 3 | 系统复位电路                     | 14  |

| 图 | 2-9.          | 惟荐外部复位电路                   | 14  |

| 图 | 2-10.         | 时钟树                        | 15  |

| 图 | 2-11.         | HXTAL 外部晶体电路               | 16  |

| 图 | 2-12.         | HXTAL 外部时钟电路(旁路模式)         | 16  |

| 图 | 2-13.         | LXTAL 外部晶体电路               | 17  |

| 图 | 2-14.         | LXTAL 外部时钟电路(旁路模式)         | 17  |

| 图 | 2-15.         | 中心扩频方式展频                   | 19  |

| 图 | 2-16.         | 向下扩频方式展频                   | 19  |

| 图 | 2-17.         | 推荐 BOOT 电路设计               | 20  |

| 图 | 2-18.         | 标准 IO 的基本结构                | 21  |

| 图 | 2-19.         | USART / UART 参考电路          | 22  |

| 图 | 2-20.         | CAN 参考电路                   | 22  |

| 图 | 2-21.         | I2C 参考电路                   | 23  |

| 图 | 2-22.         | SPI 四线模式参考电路               | 23  |

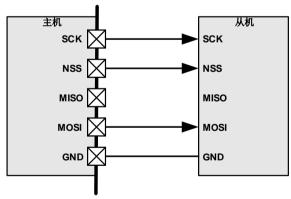

| 图 | 2-23.         | SPI 典型的全双工模式连接             | 24  |

| 图 | 2-24.         | SPI 典型的单工模式连接(主机:接收,从机:发送) | 24  |

| 图 | 2-25.         | SPI 典型的单工模式连接(主机:发送,从机:接收) | 24  |

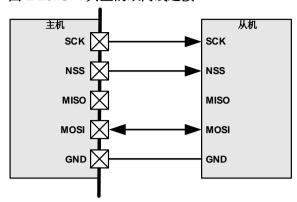

| 图 | 2-26.         | SPI 典型的双向线连接               | 25  |

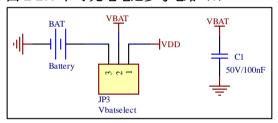

| 图 | 2-27.         | 不可充电电池参考电路(1)              | 25  |

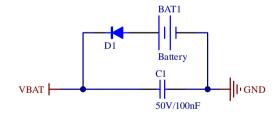

| 图 | 2-28.         | 不可充电电池参考电路(2)              | 25  |

| 图 | 2-29.         | 可充电电池参考电路                  | 25  |

| 图 | 2-30.         | ADC 采集电路设计                 | 26  |

| 图 | 2-31.         | 推荐 USBFS-Device 参考电路       | 27  |

| 图 | 2-32.         | 推荐 USBFS-Host 参考电路         | 28  |

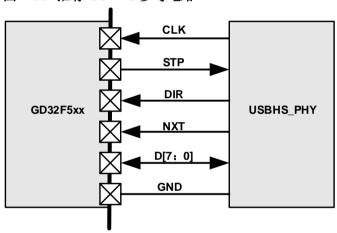

| 图 | 2-33.         | 推荐 USBHS 参考电路              | 28  |

| 图 | 2-34.         | 推荐待机模式外部唤醒引脚电路设计           | 29  |

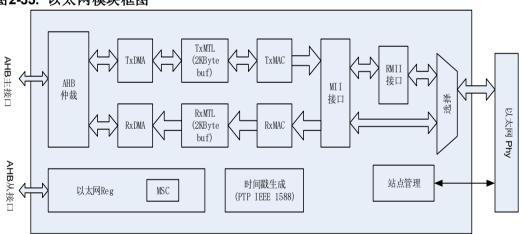

| 图 | 2-35.         | 以太网模块框图                    | 29  |

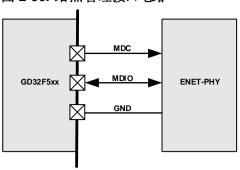

| 图 | 2-36.         | 站点管理接口电路                   | 30  |

| 图 | 2-37.         | 媒体独立接口(MII)推荐电路            | 31  |

| 图 | 2-38.         | 精简媒体独立接口(RMII)信号线          | 31  |

| 图 | 2-39.         | 推荐 JTAG 接线参考设计             | 32  |

| 囡 | 2-40          | 推荐 SWD 连线 <del>念老设计</del>  | 32  |

| Gigabevice                        |    |

|-----------------------------------|----|

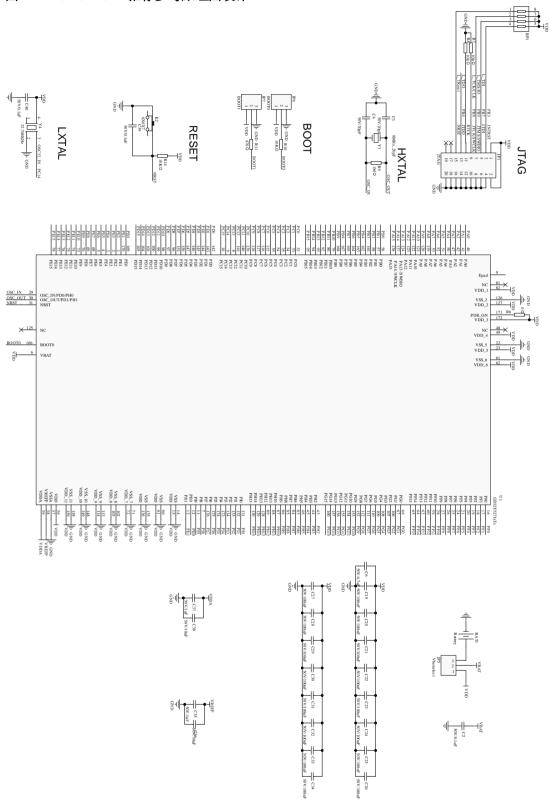

| 图 2-41. GD32F5xx 推荐参考原理图设计        | 34 |

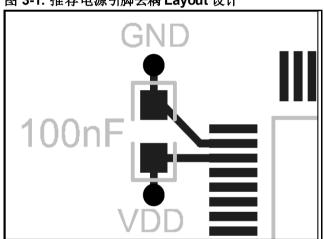

| 图 3-1. 推荐电源引脚去耦 Layout 设计         | 35 |

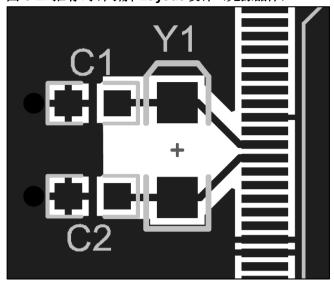

| 图 3-2. 推荐时钟引脚 Layout 设计(无源晶体)     | 36 |

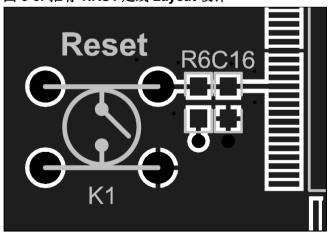

| 图 3-3. 推荐 NRST 走线 Layout 设计       | 36 |

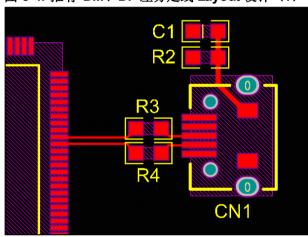

| 图 3-4. 推荐 DM、DP 差分走线 Layout 设计(1) | 37 |

| 图 3-5. 推荐 DM、DP 差分走线 Layout 设计(2) | 37 |

| 图 3-6. 推荐 MCU 与 PHY Layout 设计     | 38 |

| 图 3-7. BGA176 封装的扇出方式             | 39 |

| 图 4-1. 推荐回流焊温度曲线                  | 41 |

|                                   |    |

# 表索引

| 表 1-1. 适用产品                                                        | 7  |

|--------------------------------------------------------------------|----|

| 表 2-1. 节电模式总结                                                      |    |

| 表 2-2. RTC 的省电模式                                                   | 10 |

| 表 2-3. 不同复位类型下复位内容                                                 |    |

| 表 2-4. V <sub>BOR</sub> 阈值电压设置                                     | 13 |

| 表 2-5. 时钟输出 0 的时钟源选择                                               | 18 |

| 表 2-6. 时钟输出 1 的时钟源选择                                               | 18 |

| 表 2-7. PLL spread spectrum clock generation (SSCG) characteristics | 18 |

| 表 2-8. BOOT 模式                                                     | 20 |

| 表 2-9. 传输模式与上拉电阻参考关系                                               | 23 |

| 表 2-10. f <sub>ADC</sub> = 40MHz 采样周期与外部输入阻抗关系                     | 26 |

| 表 2-11. DAC 相关引脚描述                                                 | 27 |

| 表 2-12. 以太网信号(MII 模式)                                              | 30 |

| 表 2-13. 以太网信号(RMII 模式)                                             | 30 |

| 表 2-14. JTAG 下载调试接口分配                                              | 32 |

| 表 2-15. SWD下载调试接口分配                                                | 32 |

| 表 4-1. GD32F5xx 芯片推荐钢网厚度                                           | 40 |

| 表 4-2. 回流焊相关参数                                                     | 41 |

| 表 5-1. 封装型号说明                                                      | 42 |

| 表 6-1. 版本历史                                                        | 43 |

### 1. 前言

本文是专为基于Arm® Cortex®-M33架构的32位通用MCU GD32F5xx系列开发者提供的,对GD32F5xx系列产品硬件开发做了总体介绍,如电源、复位、时钟、启动模式的设置及下载调试等。该应用笔记的目的是让开发者快速上手使用GD32F5xx系列产品,并快速进行产品硬件开发使用,节约研读手册的时间,加快产品开发进度。

本应用笔记总共分为八部分来讲述:

- 1. 电源,主要介绍GD32F5xx系列电源管理、供电及复位功能的设计;

- 2. 时钟, 主要介绍GD32F5xx系列高、低速时钟的功能设计;

- 3. 启动配置,主要介绍GD32F5xx系列BOOT配置及设计;

- 4. 典型外设模块,主要介绍GD32F5xx系列主要功能模块硬件设计;

- 5. 下载调试电路,主要介绍GD32F5xx系列推荐典型下载调试电路;

- 6. 参考电路及PCB Layout设计,主要介绍GD32F5xx系列硬件电路设计及PCB Layout设计注意事项;

- 7. 钢网与焊接,主要介绍钢网选择与使用方法及回流焊温度曲线;

- 8. 封装说明,主要介绍GD32F5xx系列所包含的封装形式及命名。

该文档也满足了基于GD32F5xx系列产品应用开发中所用到的最小系统硬件资源。

#### 表 1-1. 适用产品

| 类型  | 型号          |

|-----|-------------|

| MCU | GD32F5xx 系列 |

#### 硬件设计 2.

#### 电源 2.1.

GD32F5xx系列V<sub>DD</sub> / V<sub>DDA</sub>工作电压范围为1.71 V - 3.6 V。如*图2-1. GD32F5xx系列电源域概* 览所示,GD32F5xx系列设备有三个电源域,包括VDD/VDDA域,1.2V域和备份域。VDD/VDDA 域由电源直接供电,且在VDD/VDDA域中嵌入了一个LDO,用来为1.2 V域供电。在备份域中有 一个电源切换器,当VDD电源关闭时,电源切换器可以将备份域的电源切换到VBAT引脚,此时 备份域由VBAT引脚(电池)供电。仅有VBAT引脚供电时,备份域的BLDO,为1.2V域的备份 SRAM供电(需PMU CS寄存器中BLDOON被置位),以保证Voo断开时,用户数据不丢失。

图2-1. GD32F5xx系列电源域概览 **VBAT** VDD **Backup Domain V**BAK Power Switch **LXTAL BPOR** 3.3V WKUPR **BLDO** RTC **WKUP BKP PAD** 1.2V **PMU** WKUPN CTL **BKPSRAM** WKUPF SLEEPING-**FWDGT** Cortex-M33 SLEEPDEEP **HXTAL** POR/PDR LDO AHB IPs APB IPs 1.2V **V**DD **Domain** 1.2 V Domain V<sub>DDA</sub> Domain IRC16M IRC32K **ADC** IRC48M VDDA 🔀 LVD **PLLs** DAC LVD: 低压检测器 LDO: 电压调节器 BPOR: 备份域上电复位 POR: 上电复位 PDR: 掉电复位 BLDO: 备份SRAM LDO输出1.2V 电压 BKPSRAM: 备份SRAM

#### 备份域 2.1.1.

备份域供电电压范围为1.71V-3.6V。电池备份域由内部电源切换器来选择VDD供电或VBAT(电 池)供电,然后由VBAK为备份域供电。为了确保备份域中寄存器的内容及RTC正常工作,当VDD 关闭时,VBAT引脚可以连接至电池或其他备份源供电。如果外部没有电池供电的应用,建议 将VBAT引脚通过100nF电容对地后接至VDD引脚上。

关于VBAT电源有以下注意事项:

关于VBAT引脚的功耗,理论上,当MCU的V<sub>DD</sub>上电时,备份域内部Swich连接到V<sub>DD</sub>上,VBAT 引脚无电流。但是,当主程序有使用ADC通过内部channel测量V<sub>BAT</sub>值时,由于MCU设计,会对V<sub>BAT</sub>进行4分压,然后进ADC channel,因此会在VBAT引脚上引起额外的功耗(几十uA级)。

#### 2.1.2. V<sub>DD</sub> / V<sub>DDA</sub> 电源域

$V_{DD}$  /  $V_{DDA}$ 电源域包括 $V_{DD}$ 域和 $V_{DDA}$ 域两部分。如果 $V_{DDA}$ 不等于 $V_{DD}$ ,要求两者之间的压差不能超过300 mV(芯片内部 $V_{DDA}$ 与 $V_{DD}$ 通过背靠背二极管连接)。为避免噪声, $V_{DDA}$ 可通过外部滤波电路连接至 $V_{DD}$ ,相应的 $V_{SSA}$ 通过特定电路(单点接地,通过 $\Omega$ 电阻或者磁珠等)连接至 $V_{SS}$ 。

为了提高ADC的转换精度,使模拟电路达到更好的特性,可为V<sub>DDA</sub>独立供电。在GD32F5xx系列产品上,含有专为ADC独立供电的V<sub>REFP</sub>(1.8 V ≤ V<sub>REFP</sub> ≤ V<sub>DDA</sub>)。

在GD32F5xx系列产品上,含有VREFP引脚(仅封装不小于100 pin的产品有VREFP引脚),VREFP引脚供电可以使用外部参考电源,也可以直连至VDDA引脚。

#### 2.1.3. 省电模式

GD32F5xx系列产品提供三种省电模式,分别是睡眠模式、深度睡眠模式和待机模式,三种省电模式对比如*表2-1. 节电模式总结*所示。

表 2-1. 节电模式总结

| 模式     | 睡眠                                                                                 | 深度睡眠                                                                            | 待机                                             |

|--------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------|

| 描述     | 仅关闭 CPU 时钟                                                                         | 1、关闭 1.2V 电源域的所有时钟<br>2、关闭 IRC16M、HXTAL 和 PLL                                   | 1、关闭 1.2V 电源域的供电<br>2、关闭 IRC16M、HXTAL<br>和 PLL |

| LDO 状态 | 开启(正常功耗,正常驱<br>动模式)                                                                | 开启(正常功耗或低功耗模式,<br>正常驱动或低驱动模式)                                                   | 关闭                                             |

| 配置     | SLEEPDEEP = 0                                                                      | SLEEPDE EP = 1<br>STBMOD = 0                                                    | SLEEPDE EP = 1<br>STBMOD = 1, WURST=1          |

| 进入指令   | WFI 或 WFE                                                                          | WFI 或 WFE                                                                       | WFI 或 WFE                                      |

| 唤醒     | 若通过 WFI 进入,则任何<br>中断均可唤醒;<br>若通过 WFE 进入,则任<br>何事件(或<br>SEVONPEND = 1 时的中<br>断)均可唤醒 | 若通过 WFI 进入,来自 EXTI 的任何中断可唤醒;若通过 WFE 进入,来自 EXTI 的任何事件(或 SEV ONPEN D = 1 时的中断)可唤醒 | 1、NRST 引脚<br>2、WKUP 引脚<br>3、FWDGT 复位<br>4、RTC  |

| 唤醒延迟   | 无                                                                                  | IRC16M 唤醒时间<br>如果 LDO 处于低功耗模式,需增<br>加 LDO 唤醒时间                                  | 上电序列                                           |

**备注:** 在待机模式下,除 NRST 引脚、配置为 RTC 功能的 PC13 和 PI8、用作 LXTAL 晶振引脚的 PC14 和 PC15、使能的 WKUP 引脚外,其他所有 I/O 都处于高阻态。

针对RTC的省电模式,见表2-2. RTC的省电模式。

#### 表 2-2. RTC 的省电模式

| 模式     | 模式下能否工作                | 退出该模式的方法              |

|--------|------------------------|-----------------------|

| 睡眠模式   | 是                      | RTC中断                 |

| 深度睡眠模式 | 当时钟源是LXTAL或IRC32K时可以工作 | RTC闹钟/侵入事件/时间戳事件/唤醒事件 |

| 待机模式   | 当时钟源是LXTAL或IRC32K时可以工作 | RTC闹钟/侵入事件/时间戳事件/唤醒事件 |

### 2.1.4. 供电设计

系统需要稳定的电源,开发使用的时候有些重要事项需要注意:

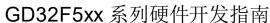

- VDD引脚必须外接对地电容(N\*100nF陶瓷电容+不小于4.7 µF钽电容,至少一个 VDD引脚需要接不小于4.7 µF电容到GND,其他VDD引脚接100 nF);

- VDDA引脚必须外接对地电容(建议10 nF + 1 µF陶瓷电容);

- V<sub>REFP</sub>电压可由内部产生也可直连至V<sub>DDA</sub>,且在VREFP引脚对地连接10 nF + 1 μF陶瓷电容。

#### 图 2-2. GD32F5xx 系列推荐供电设

#### 注意:

- 1. 所有去耦电容须靠近芯片对应VDD、VDDA、VREFP引脚放置;

- 2. 当MCU电源电压不稳定,或有电压跌落等风险时,建议将V<sub>DD</sub>的4.7 μF电容调整为不低于 10 μF的电容。

#### 2.1.5. 复位及电源管理

GD32F5xx复位控制包括三种控制方式:电源复位、系统复位和备份域复位。电源复位又称为冷复位,其复位除了备份域的所有系统。系统复位将复位除了SW-DP控制器和备份域之外的其余部分,包括处理器内核和外设IP。备份域复位将复位备份区域。复位能够被外部信号、内部事件和复位发生器触发。

表 2-3. 不同复位类型下复位内容

| 复位方式       | 电源复位       | 系统复位               | 备份域复位 |

|------------|------------|--------------------|-------|

| 复位内容       | 除了备份域的所有系统 | 除了SW-DP控制器和备份域之外的其 | 备份区域  |

| <b>交应的</b> |            | 余部分,包括处理器内核和外设IP   | 田历区场  |

电源和系统复位的过程中,NRST会维持一个低电平,直至复位结束。MCU无法执行起来时,可以通过示波器监测NRST引脚波形,来判断芯片是否有一直发生复位事件。

#### VDDA域

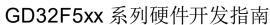

芯片内部集成 POR/PDR(上电/掉电复位)电路,用于检测 V<sub>DDA</sub>,并在电压低于特定阈值时产生电源复位信号,复位除备份域之外的整个芯片。V<sub>POR</sub> 表示上电复位的阈值电压,典型值约为 1.68 V<sub>1</sub> V<sub>PDR</sub> 表示掉电复位的阈值电压,典型值约为 1.64 V<sub>2</sub> 迟滞电压 V<sub>Inst</sub> 值约为 40 mV<sub>2</sub>

#### 图2-3. 上电 / 掉电复位波形图

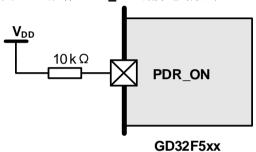

**注意**: PDR\_ON引脚仅存在于不小于144 pin封装上。内部POR / PDR电路由PDR\_ON引脚使能。为了保证芯片上电和下电阶段POR / PDR的有效性,建议将PDR\_ON引脚通过10 k $\Omega$ 电阻拉到 $V_{DD}$ 上。

#### VDD域

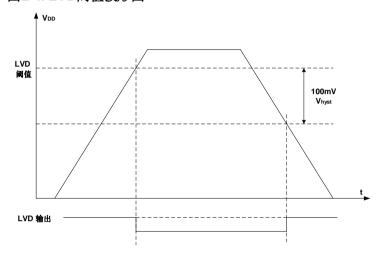

LVD的功能是检测V<sub>DD</sub>供电电压是否低于低电压检测阈值,该阈值由电源控制寄存器 (PMU CTL)中的LVDT[2:0]位进行配置。LVD通过LVDEN置位使能,位于电源状态寄存器

(PMU\_CS)中的LVDF位表示低电压事件是否出现,该事件连接至EXTI的第16线,用户可以通过配置EXTI的第16线产生相应的中断。**图2-4. LVD阈值波形图**显示了V<sub>DD</sub>供电电压和LVD输出信号的关系。(LVD中断信号依赖于EXTI第16线的上升或下降沿配置)。迟滞电压V<sub>Dvst</sub>为100 mV。

LVD 应用场合: 当 MCU 电源受到外部干扰时,如发生电压跌落,我们可通过 LVD 设置低电压检测阈值(该阈值大于 PDR 值),一旦跌落到该阈值,LVD 中断被打开,可在中断函数里设置软复位等操作,避免 MCU 发生其他异常。

#### 图2-4. LVD阈值波形图

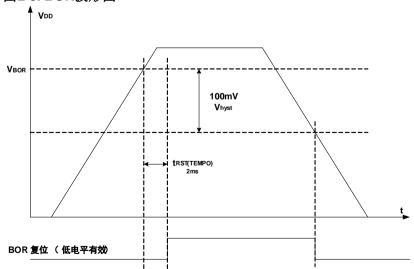

GD32F5xx系列MCU内部还集成有BOR电路。BOR电路检测 $V_{DD}$ 电压,并在其电压低于选项字节的BOR\_TH定义的阈值且该阈值不为0b11(BOR\_TH=0b11,BOR功能关闭)时,产生电源复位信号,复位除备份域外的整个芯片。不管选项字节BOR\_TH的值是否为0b11,POR/PDR(上电/掉电复位)电路会一直处于检测状态。**图2-5. BOR波形图**显示了,供电电压和BOR复位信号之间的关系。 $V_{BOR}$ 表示BOR复位的阈值电压,该阈值在选项字节BOR\_TH中定义。 $V_{BOR}$ 迟滞电压 $V_{hest}$ 值为100 mV。

图2-5. BOR波形图

BOR阈值通过选项字节BOR\_TH设置,可以设置三种不同的level,对应关系参照<u>表2-4. VBOR</u> 阈值电压设置:

| 寿   | 2-4          | V | DOD. | 圀     | 佶  | 由  | 压设置       |  |

|-----|--------------|---|------|-------|----|----|-----------|--|

| AX. | <b>4-4</b> . | v | RUR  | 12341 | 10 | ж. | / IN PX 😑 |  |

| Symbol                  | Conditions   | Тур   |

|-------------------------|--------------|-------|

| DOD TH 00/DOD love(2)   | Falling edge | 2.8 V |

| BOR_TH=00(BOR level3)   | Rising edge  | 2.9 V |

| DOD TH 04/DOD (0)(0)(2) | Falling edge | 2.5 V |

| BOR_TH=01(BOR level2)   | Rising edge  | 2.6 V |

| BOR TH=10(BOR level1)   | Falling edge | 2.2 V |

| BOR_THETO(BOR levelt)   | Rising edge  | 2.3 V |

| BOR_TH=11(BOR off)      | -            | -     |

GD32F5xx系列产品中,LQFP176、BGA176和LQFP144封装产品有PDR\_ON引脚,该引脚使能芯片内部POR/PDR电路。为确保芯片在上电阶段与掉电阶段发生有效POR与PDR,该pin 需上拉,可通过一个10 k $\Omega$ 电阻上拉到 $V_{DD}$ ,如**图2-6.** 推荐PDR\_ON引脚电路设计所示。

图 2-6. 推荐 PDR\_ON 引脚电路设计

另外,MCU复位源可以通过查询寄存器RCU\_RSTSCK获取,该寄存器只有上电复位,才能清除标志位。所以在使用过程中,获取到复位源后,可通过RSTFC控制位清除复位标志。之后再发生看门狗复位或其他复位事件时,才能较准确的在RCU\_RSTSCK寄存器中体现出来。

图 2-7. RCU\_RSTSCK 寄存器

| 31   | 30     | 29    | 28   | 27   | 26   | 25   | 24    | 23 | 22 | 21 | 20  | 19 | 18 | 17     | 16       |

|------|--------|-------|------|------|------|------|-------|----|----|----|-----|----|----|--------|----------|

| LP   | WWDGTR | FWDGT | sw   | POR  | EP   | BOR  | RSTFC |    |    |    | 保   | in |    |        |          |

| RSTF | STF    | RSTF  | RSTF | RSTF | RSTF | RSTF | KSIFC |    |    |    | 17K | ₩  |    |        |          |

| r    | r      | r     | r    | r    | r    | r    | rw    |    |    |    |     |    |    |        |          |

| 15   | 14     | 13    | 12   | 11   | 10   | 9    | 8     | 7  | 6  | 5  | 4   | 3  | 2  | 1      | 0        |

|      |        |       |      |      |      | JQ.  | 留     |    |    |    |     |    |    | IRC32K | IRC32KEN |

|      |        |       |      |      |      | D#   | · III |    |    |    |     |    |    | STB    | IRUSZKEN |

|      |        |       |      |      |      |      |       |    |    |    |     |    |    | г      | rw       |

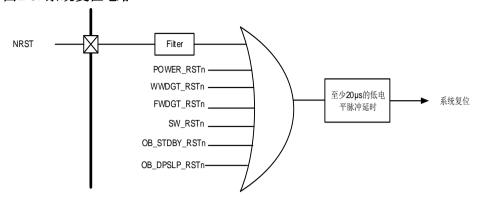

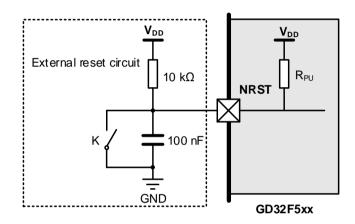

MCU内部集成有上电/掉电复位电路,在设计外部复位电路时,NRST管脚必须要放置一个电容(典型值100 nF),确保NRST管脚上电能产生一个至少20 us的低脉冲延时,完成有效上电复位过程。

#### 图2-8. 系统复位电路

图 2-9. 推荐外部复位电路

#### 注意:

- 1. 上拉电阻建议10 kΩ即可,以使得电压干扰不会导致芯片工作异常;

- 2. 若考虑静电等影响,可在NRST管脚处放置ESD保护二极管;

- 3. 尽管MCU内部有硬件POR电路,仍推荐外部加NRST复位阻容电路;

- 4. 如果MCU启动异常(由于电压波动等),可适当增加NRST对地电容值,拉长MCU复位完成时间,避开上电异常时序区;

- 5. 当备份域复位时,BKPSRAM域不会复位。

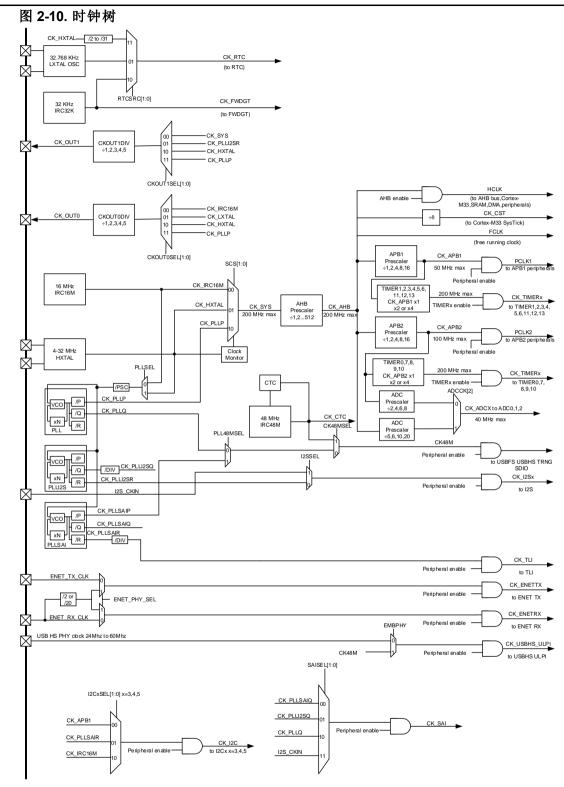

### 2.2. 时钟

GD32F5xx系列内部有完备的时钟系统,可以根据不同的应用场合,选择合适的时钟源。时钟主要特征:

- 4到32 MHz外部高速晶体振荡器(HXTAL)

- 内部16 MHz RC振荡器(IRC16M)

- 内部48 MHz RC振荡器(IRC48M)

- 32.768 kHz外部低速晶体振荡器 (LXTAL)

- 内部32 kHz RC振荡器(IRC32K)

- PLL时钟源可选HXTAL或IRC16M

- HXTAL时钟监视器

注意: GD32F5xx系列MCU最高主频为200 MHz。

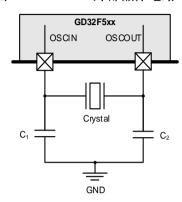

#### 2.2.1. 外部高速晶体振荡时钟(HXTAL)

4-32 MHz外部高速晶体振荡器(无源晶体),可为系统提供精准的主时钟。该特定频率的晶体必须靠近HXTAL引脚放置,和晶体连接的外部电阻和匹配电容,必须根据所选择的振荡器参

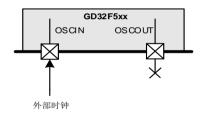

数来调整。HXTAL还可以使用旁路输入的模式来输入时钟源(1 – 50 MHz有源晶振等)。旁路输入时,信号接至OSC\_IN引脚,OSC\_OUT引脚保持悬空状态,软件上需要打开HXTAL的Bypass功能(控制寄存器RCU\_CTL的HXTALBPS和HXTALEN位置'1')。

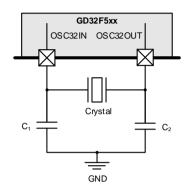

#### 图 2-11. HXTAL 外部晶体电路

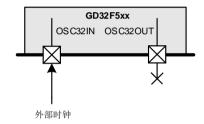

图 2-12. HXTAL 外部时钟电路 (旁路模式)

#### 注意:

- 1. 使用旁路输入时,信号从OSC IN输入,OSC OUT保持悬空状态;

- 2. 关于外部匹配电容大小可参考公式:  $C_1 = C_2 = 2*(C_{LOAD} C_s)$ ,其中 $C_s$ 为PCB和MCU引脚的杂散电容,典型值为10 pF。推荐选用外部高速晶体时,尽量选择晶体负载电容在20 pF左右的,这样外部所接匹配电容 $C_1$ 和 $C_2$ 电容值为20 pF即可,且PCB Layout时尽可能近地靠近晶振引脚:

- 3. C<sub>s</sub>为PCB板走线及IC pin上的寄生电容,当晶体离MCU越近,C<sub>s</sub>越小,反之越大。所以,在实际应用中,当晶体离MCU较远导致晶体工作异常时,可适当减小外部匹配电容;

- 4. 使用外部高速晶体时,建议在晶体两端并联1MΩ电阻,以使得晶体更容易起振;

- 5. 精度:外部有源晶振 > 外部无源晶体 > 内部IRC16M;

- 6. 正常使用有源晶振,会打开Bypass,此时要求高电平不低于0.7V<sub>DD</sub>,低电平不大于0.3V<sub>DD</sub>。 如不打开Bypass,对有源晶振的振幅幅值要求会大大降低;

- 7. 谐振器与MCU时钟引脚连接的走线,即连接到MCU的OSC\_OUT和OSC\_IN两个引脚的走线,可能会因为PCB布局布线的空间限制,导致长度不一致。这会使两条PCB走线引入的杂散电容不一致,从而导致谐振器两边的负载电容在取值时不相等,需要存在差值,以匹配实际的PCB板。对于这种情况,建议联系谐振器厂家,测算实际的数值。

#### 2.2.2. 外部低速晶体振荡时钟(LXTAL)

LXTAL晶体是一个32.768 kHz的低速外部晶体(无源晶体),能够为RTC提供一个低功耗且高精度的时钟源。MCU的RTC模块相当于一个计数器,精度会受到晶体性能、匹配电容以及PCB

材质等影响。如果想要获取到较好精度,在电路设计时,建议将PC13接至定时器输入捕获管脚,通过TIMER来对LXTAL进行校准,根据校准情况设定RTC的分频寄存器。LXTAL也可以支持旁路时钟输入(有源晶振等),可以通过配置RCU\_BDCTL里面的LXTALBPS和LXTALEN位来使能。

#### 图 2-13. LXTAL 外部晶体电路

图 2-14. LXTAL 外部时钟电路 (旁路模式)

#### 注意:

- 1. 使用旁路输入时,信号从OSC32 IN引脚输入,OSC32 OUT引脚保持悬空状态;

- 2. 关于外部匹配电容大小可参考公式:  $C_1 = C_2 = 2*(C_{LOAD} C_s)$ ,其中 $C_s$ 为PCB和MCU引脚的杂散电容,经验值在2pF 7pF之间,建议以5pF为参考值计算。推荐选用外部晶体时,尽量选择晶体负载电容在10pF左右的,这样外部所接匹配电容 $C_1$ 和 $C_2$ 电容值为10pF即可,且PCB Layout时尽可能近地靠近晶振引脚。

- 3. 当RTC选择IRC32K作为时钟源,并且V<sub>BAT</sub>外部独立供电时,如果此时MCU掉电,RTC会停止计数。重新上电后,RTC会接着之前的计数值,继续累加计时。若需要V<sub>BAT</sub>外部独立给RTC供电,且MCU掉电后,RTC仍能正常计时,RTC须选择LXTAL作为时钟源。

- 4. MCU可以设置LXTAL的驱动能力。若实际调试过程中,发现外部低速晶体难以起振,可尝试将LXTAL的驱动能力调整为高驱动能力。

- 5. 谐振器与MCU时钟引脚连接的走线,即连接到MCU的OSC\_OUT和OSC\_IN两个引脚的走线,可能会应为PCB布局布线的空间限制,导致长度不一致。这会使两条PCB走线引入的杂散电容不一致,从而导致谐振器两边的负载电容在取值时不能相等,需要存在差值以匹配实际的PCB板。对于这种情况,建议联系谐振器厂家,测算实际的数值。

#### 2.2.3. 时钟输出能力(CKOUT)

GD32F5xx系列MCU可输出32 kHz到200 MHz的时钟信号。通过设置时钟配置寄存器0(RCU CFG0)中的CK OUT0时钟源选择位域CKOUT0SEL,能够选择不同的时钟信号。

CK\_OUT1时钟输出源的选择,通过设置时钟配置寄存器RCU\_CFG0中的CKOUT1SEL位域实现。相应的GPIO引脚,应该被配置成备用功能I/O(AFIO)模式,来输出选择的时钟信号。CK OUT0对应的IO口为PA8,CK OUT1对应的IO口为PC9。

表 2-5. 时钟输出 0 的时钟源选择

| 时钟输出 0 的时钟源选择位域 | 时钟源       |

|-----------------|-----------|

| 00              | CK_IRC16M |

| 01              | CK_LXTAL  |

| 10              | CK_HXTAL  |

| 11              | CK_PLLP   |

表 2-6. 时钟输出1的时钟源选择

| 时钟输出 1 的时钟源选择位域 | 时钟源        |

|-----------------|------------|

| 00              | CK_SYS     |

| 01              | CK_PLLI2SR |

| 10              | CK_HXTAL   |

| 11              | CK_PLLP    |

#### 2.2.4. HXTAL 时钟监视器 (CKM)

可以通过设置控制寄存器RCU\_CTL中的HXTAL时钟监视使能位CKMEN,使能HXTAL时钟监视功能。该功能必须在HXTAL启动延迟完毕后使能,在HXTAL停止后禁止。一旦监测到HXTAL故障,HXTAL将自动被禁止,中断寄存器RCU\_INT中的HXTAL时钟阻塞中断标志位CKMIF将被置'1',产生HXTAL故障事件。这个故障引发的中断,和Cortex®-M33的不可屏蔽中断NMI相连。如果HXTAL被选作系统或PLL的时钟源,HXTAL故障将促使选择IRC16M为系统时钟源且PLL将被自动禁止。

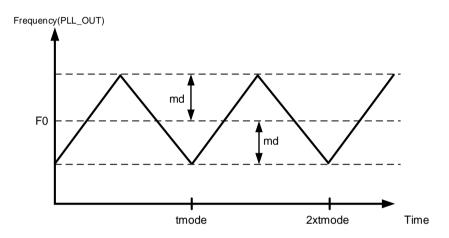

#### 2.2.5. PLL 展频(SSCG)

为了减小EMI干扰,GD32F5xx系列PLL集成了时钟展频功能(只适用于主PLL),有效降低了PLL在主时钟频点及其奇次谐波的能量。根据设置的调制频率f<sub>mod</sub>与调制峰值mdamp(范围参照*表2-7. PLL spread spectrum clock generation (SSCG) characteristics*),通过公式(2-1)与公式(2-2),计算出MODCNT与MODSTEP,填入PLL时钟扩频控制寄存器(RCU\_PLLSSCTL)中,注意MODCNT与MODSTEP的乘积不能大于2^15-1,如果出现大于的情况,则需要降低调制峰值Mdamp重新计算。

表 2-7. PLL spread spectrum clock generation (SSCG) characteristics

| Symbol           | Parameter                 | Conditions | Min | Тур | Max                | Unit |

|------------------|---------------------------|------------|-----|-----|--------------------|------|

| f <sub>mod</sub> | Modulation frequency      |            | _   | _   | 10                 | kHz  |

| mdamp            | Peak modulation amplitude |            | _   | _   | 2                  | %    |

| MODCNT* MODSTEP  | _                         | _          | _   |     | 2 <sup>15</sup> -1 | _    |

MODCNT与MODSTEP通过以下算式得出:

$$MODCNT = round(f_{PLLIN}/4/f_{mod})$$

(2-1)

$$MODSTEP = round(mdamp*PLLN*2^{14}/(MODCNT*100))$$

(2-2)

f<sub>PLLIN</sub>表示PLL输入时钟频率,f<sub>mod</sub>表示扩频调制频率,mdamp表示扩频调制振幅(按百分比表示),PLLN表示PLL时钟频率倍频因子

例如PLL参考时钟源HXTAL = 8 MHz,预分频PLLM = 4,则 $f_{PLLIN}$  = 2 MHz,设置PLLN = 200 (此时VCO频率400 MHz,二分频得到系统时钟200 MHz),展频调制频率10 kHz,调制幅度 2%,则计算得到MODCNT = 50,MODSTEP = 1311,此时MODCNT\*MODSTEP >  $2^{15}$ -1,无法达到。如降低调制幅度为1%,则MODCNT = 50,MODSTEP = 655,此时MODCNT\*MODSTEP = 32750 <  $2^{15}$ -1满足要求。

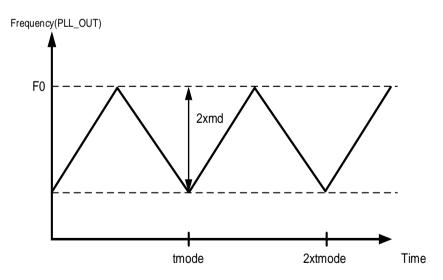

根据寄存器RCU\_PLLSSCTL中SS\_TYPE的设置,可选择两种扩频调制类型,分别为中心扩频和向下扩频,PLL输出频率会按如下波形变化。

#### 图 2-15. 中心扩频方式展频

图 2-16. 向下扩频方式展频

注意:如果使能了PLL展频功能,则系统时钟频率则会处于波动状态,对于时钟精度要求较高的外设,则可能发生工作不正常的情况。如,使用MCU IO输出时钟信号,作为USB或以太网PHY的时钟源,PHY可能工作不正常。USB可以使用内部48 MHz时钟(建议进行CTC校准),或者连接高速PHY,搭载外部时钟;以太网必须使用外部时钟。

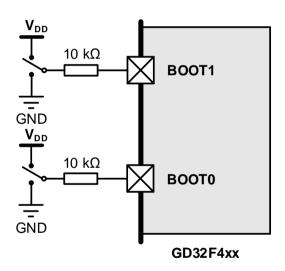

### 2.3. 启动配置

GD32F5xx系列提供三种启动方式,可以通过BOOT0位和BOOT1引脚进行选择来确定启动选项。电路设计时,若要运行用户程序,BOOT0引脚不能悬空,建议通过一个10kΩ电阻到GND;运行System Memory进行程序更新,需要将BOOT0引脚接高,BOOT1引脚接低,更新完成后,再将BOOT0接低后上电才能运行用户程序;SRAM执行程序多用于调试状态下。

嵌入式的Bootloader存放在系统存储空间,用于对FLASH存储器进行重新编程。Bootloader可以通过USART0(PA9和PA10)、USART2(PB10和PB11,PC10和PC11,PE8和PD15)或USBFS(PA11和PA12)从机模式和外界交互。

表 2-8. BOOT 模式

| BOOT 模式           | BOOT1 | воото |

|-------------------|-------|-------|

| Main Flash Memory | X     | 0     |

| System Memory     | 0     | 1     |

| On Chip SRAM      | 1     | 1     |

图 2-17. 推荐 BOOT 电路设计

#### 注意:

- 1. MCU运行后,如果改变BOOT状态,须系统复位后才可生效;

- 2. 一旦BOOT1引脚状态被采样到,它可以被释放用于其他用途。

## 2.4. 典型外设模块

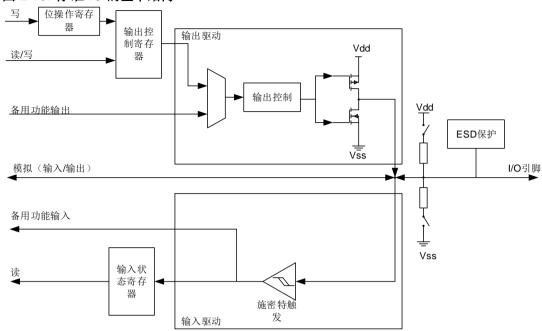

#### 2.4.1. GPIO 电路

GD32F5xx最多可支持140个通用I/O引脚(GPIO),分别为PA0~PA15,PB0~PB15,PC0~PC15,PD0~PD15,PE0~PE15,PF0~PF15,PG0~PG15,PH0~PH15,PI0~PI11;每个引脚都可以通过寄存器独立配置,GPIO口的基本结构详见*图2-18. 标准IO的基本结构*:

#### 图 2-18. 标准 IO 的基本结构

#### 注意:

- 1. IO口分为5V耐受和非5V耐受,使用时注意区分IO口耐压情况,对于GD32F5xx系列芯片,除去PA4,PA5这2个pin为非5V耐受pin,其余pin脚均为5V耐受脚;

- 2. 5V耐受的IO口直接5 V时,建议IO口配置为开漏模式,输出高电平通过外部上拉实现;

- 3. 每个GPIO引脚可以由软件配置为输出(推挽或开漏)、输入、外设备用功能或者模拟模式;

- 4. 在复位期间或复位之后,备用功能并未激活,所有GPIO端口都被配置成输入浮空模式,这种输入模式禁用上拉(PU)/下拉(PD)电阻。为了获得较一致的功耗,建议所有IO口配置成模拟输入,然后再根据应用需求,修改为相应的模式(芯片内部没有引出的端口也需要配置);

- 5. 为提高EMC性能,未使用的IO口引脚建议硬件上拉或者是下拉;

- 6. PC13、PC14、PC15和PI8这四个IO口的驱动能力偏弱,输出电流能力有限,配置为输出模式时,其工作速度不能超过2MHz:

- 7. 只有在输入模式下配置,端口才能使用外部中断/事件线;

- 8. 需要连接板外器件或者开关、按键的引脚,建议在紧靠对外端加上ESD防护电路。

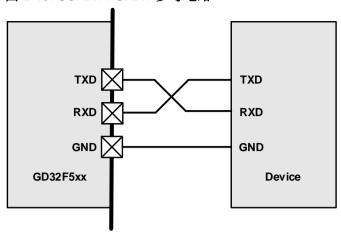

#### 2.4.2. USART / UART 电路

GD32F5xx系列产品提供4路USART(USART0, USART1, USART2, USART5)和4路UART(UART3, UART4, UART6, UART7)。在使用USART/UART时,注意引脚的交叉相连,<u>图2-19. USART/UART参考电路</u>可供参考。

#### 图 2-19. USART / UART 参考电路

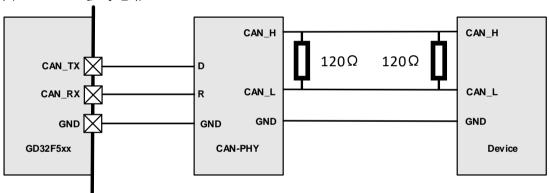

#### 2.4.3. CAN 电路

GD32F5xx系列芯片提供2路CAN通信外设(CAN0和CAN1),**图2-20.** *CAN参考电路*可供参考。

#### 图 2-20. CAN 参考电路

上图中两个 $120\Omega$ 的阻抗匹配电阻,可根据实际情况决定阻抗匹配电阻阻值及其是否需要。

在CAN通信中,阻抗匹配的作用有三个:

- 1.提高抗干扰能力;

- 2.防止信号反射,提高信号质量;

- 3.确保总线上升/下降沿快速达到。

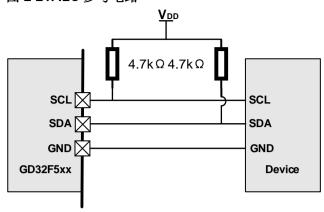

#### 2.4.4. I2C 电路

GD32F5xx系列芯片提供6路I2C外设,其中,I2C0、I2C1、I2C2支持标准模式(最高100kHz)和快速模式(最高400kHz)。I2C3、I2C4、I2C5除了标准模式和快速模式外,还支持快速+模式(最高1MHz,必须在SYSCFG\_CFG1中使能I2CxFMP(x=3,4,5))。SDA和SCL都是双向线,所有I2C通道都可以工作在主机或者从机模式。同时,也支持多主机模式。I2C接口模块也支持DMA模式,可有效减轻CPU的负担。

图 2-21. I2C 参考电路

如需连接到I2C总线设备的输出极,考虑到线与,则需空闲时电平置高。

针对OC/OD电路,电路反应速度和功耗由上拉电阻决定。上拉电阻小,则反应速度快,信号 边沿陡峭,即信号质量好,但是功耗高。反之,若上拉电阻大,则电路反应速度慢,信号边沿 较为平缓,即信号质量差,但是功耗低。

表 2-9. 传输模式与上拉电阻参考关系

| 传输模式  | 上拉电阻(kΩ) |

|-------|----------|

| 标准模式  | 4.7      |

| 快速模式  | 2.2      |

| 快速+模式 | 1.5      |

考虑到I2C实际走线和电路板上情况的复杂多样,<u>表2-9. 传输模式与上拉电阻参考关系</u>中上拉电阻值仅供参考。在实际使用时,可结合在SDA与SCL之间加入串组,以调节信号质量。

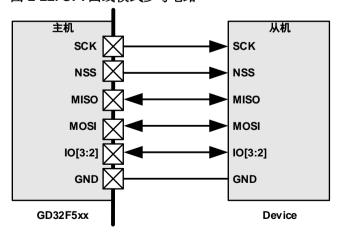

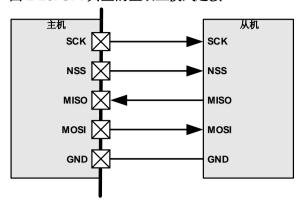

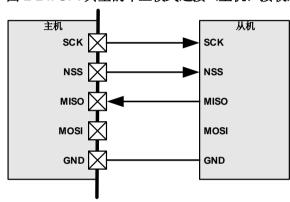

#### 2.4.5. SPI 电路

GD32F5xx系列芯片提供6路SPI,其中,SPI5可以通过寄存器配置,扩展为四线模式。除4线模式SPI外,所有SPI通道都可以工作在主机或者从机模式。SPI5工作在四线模式时,只能作为主机,不能作为从机;不工作在4线模式时,可以作为从机。

图 2-22. SPI 四线模式参考电路

上图为仅在SPI5工作在4线模式时才可参考,且此时GD32F5xx系列芯片只能作为主机。针对一般的SPI,寄存器进行适当的配置后,有以下四种典型的工作模式连接方法供参考。在以下

四种工作模式中,GD32F5xx系列芯片都可以作为主机或者从机。

#### 图 2-23. SPI 典型的全双工模式连接

图 2-24. SPI 典型的单工模式连接(主机:接收,从机:发送)

图 2-25. SPI 典型的单工模式连接(主机:发送,从机:接收)

#### 图 2-26. SPI 典型的双向线连接

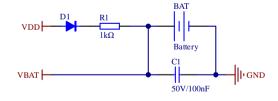

### 2.4.6. Battery 电路

GD32F5xx系列芯片含有VBAT引脚,在V<sub>DD</sub>掉电时,通过给VBAT引脚供电,可保持芯片备份域正常工作。当使用外部电池为VBAT引脚供电时,以下电路供参考。

#### 图 2-27. 不可充电电池参考电路 (1)

图 2-28. 不可充电电池参考电路(2)

图 2-29. 可充电电池参考电路

参考以上电路时,请注意电池电压、二极管压降和VBAT引脚的供电电压范围,避免出现过压或欠压的现象。针对可充电电池的参考电路中电阻,其阻值根据电池特性选择。

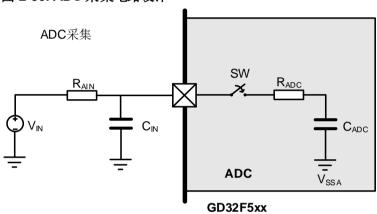

#### 2.4.7. ADC 电路

GD32F5xx系列内部集成了一个12位的SARADC,它有多达19个通道,可测量16个外部和2个内部信号源及1个外部电池电压(V<sub>BAT</sub>)监测信号源。内部信号为温度传感器通道(ADC0 CH16),

内部参考电压输入通道(ADC0\_CH17),外部信号为外部监测电池V<sub>BAT</sub>供电引脚输入通道(ADC0\_CH18)。温度传感器体现的是温度的变化,并不适合测量绝对温度。如果需要测量精确的温度,必须使用一个外置的温度传感器。内部参考电压V<sub>REFINT</sub>提供了一个稳定的电压输出(1.2 V)给到ADC,并内部连接至ADC0\_CH17。提供外部检测V<sub>BAT</sub>引脚电池电压功能,其转换的值为V<sub>BAT</sub>/4。

如果在使用过程中,ADC采集外部输入电压,若采样数据波动较大,可能是由于电源波动引起的干扰,可通过采样内部V<sub>REFINT</sub>进行校准,反推外部采样电压。

设计ADC电路时,建议在ADC输入管脚处放置个小电容,建议放置一个500 pF的小电容即可。

#### 图 2-30. ADC 采集电路设计

为了获得较好的转换结果,使用过程中,建议尽量降低fac的频率,采样周期尽量选较大的值,外部电路设计时也尽量减小输入阻抗,必要时采用运放跟随来降低输入阻抗。fac = 40 MHz时,输入阻抗和采样周期关系如下。

T<sub>s</sub> (cycles) R<sub>AIN max</sub> (kΩ) ts (us) 0.075 0.55 15 0.375 4.65 28 0.7 9.15 55 1.375 18.43 84 2.1 28.46 2.8 38.1 112 144 3.6 49.17

12

表 2-10. fadc = 40MHz 采样周期与外部输入阻抗关系

#### 2.4.8. DAC 电路

480

GD32F5xx 系列 MCU 的数字/模拟转换器,可以将 12 位的数字数据,转换为外部引脚上的电压输出。数据可以采用 8 位或 12 位模式,左对齐或右对齐模式。当使能了外部触发,DMA 可被用于更新输入端数字数据。在输出电压时,可以利用使能 DAC 输出缓冲区来获得更高的驱动能力。每个 DAC 的两个通道可以独立或并发工作。

N/A

| 表2-11. DAC相 | <b>关引脚描述</b> |

|-------------|--------------|

|-------------|--------------|

| 名称                | 描述                                            | 信号类型       |

|-------------------|-----------------------------------------------|------------|

| $V_{DDA}$         | 模拟电源                                          | 输入,模拟电源    |

| V <sub>SSA</sub>  | 模拟电源地                                         | 输入,模拟电源地   |

| V                 | DAC 正参考电压,                                    | 输入,模拟正参考电压 |

| V <sub>REFP</sub> | 1.71 V ≤ V <sub>REFP</sub> ≤ V <sub>DDA</sub> | <b>和八,</b> |

| DAC_OUTx          | DACx 模拟输出                                     | 模拟输出信号     |

在使能DAC模块前,GPIO口应配置为模拟模式。

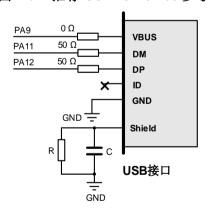

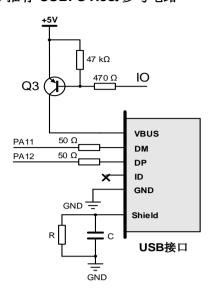

#### 2.4.9. USB 电路

GD32F5xx系列MCU拥有两种USB接口,其为一个USBFS接口,另一个为USBHS接口。USBFS包含了一个内部的全速USB PHY,并且不再需要外部PHY芯片。USBHS为外部USB物理层(PHY)提供了一个ULPI接口,并且其也包含了一个内部的全速USB PHY。所以,对于全速操作,不再需要外部的USB PHY,若使用外部高速ULPI PHY,USBHS支持的最大速度为高速。

USB协议要求时钟精度不低于500ppm,内部时钟可能无法达到这样的精度,所以建议使用USB功能时使用外部晶体或有源晶振做为USB模块时钟源。

GD32F5xx系列USB既可设计为USB device,又可设计为USB host。配置为Device时,若USBFS\_GCCFG 寄存器中VBUSIG 控制位配置为1,则PA9无需连接至V<sub>BUS</sub>线,若USBFS\_GCCFG寄存器中VBUSIG控制位配置为0,则PA9必须连接至V<sub>BUS</sub>线。

在设计电路时,为了提升USB的ESD性能,USB外壳建议设计阻容放电隔离电路。

图 2-31. 推荐 USBFS-Device 参考电路

推荐: R=1 MΩ, C=4700 pF。

#### 图 2-32. 推荐 USBFS-Host 参考电路

推荐: R=1 MΩ, C=4700 pF。

图 2-33. 推荐 USBHS 参考电路

#### 2.4.10. 待机模式唤醒电路

GD32F5xx系列支持三种低功耗模式,分别为睡眠模式,深度睡眠模式和待机模式,其中功耗最低的是待机模式(Standby模式),此低功耗模式需要的唤醒时间也是最长的。从待机模式唤醒可通过WKUP引脚上升沿唤醒,此时无需配置对应GPIO,仅需配置PMU\_CS寄存器里的WUPEN位即可。对应WKUP唤醒引脚参考电路设计如下:

#### 图 2-34. 推荐待机模式外部唤醒引脚电路设计

**注意:** 该模式在电路设计时需要注意,WKUP引脚至V<sub>DD</sub>间如果有串电阻,可能会增加额外的功耗。

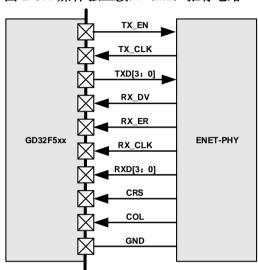

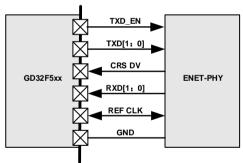

#### 2.4.11. Ethernet 电路

GD32F5xx系列产品支持以太网外设,该模块包含10/100Mbps以太网MAC(媒体访问控制器),采用DMA优化数据帧的发送与接收性能,支持MII(媒体独立接口)与RMII(简化的媒体独立接口)两种与物理层(PHY)通讯的标准接口,实现以太网数据帧的发送与接收。以太网模块遵守IEEE 802.3-2002标准和IEEE 1588-2008标准。

图2-35. 以太网模块框图

在使用以太网模块时,用户应确保配置的时钟频率不小于25 MHz。

以太网外设中,站点管理接口(SMI)用于访问和设置PHY的配置,通过MDC时钟线与MDIO数据线与外部PHY通讯,可以通过其访问任意PHY的任意寄存器。SMI接口支持的最大PHY数量为32,但在同一时刻只能访问一个PHY的一个寄存器。MDC时钟线和MDIO数据线具体作用如下:

- MDC:最高频率为2.5 MHz的时钟信号,在空闲状态下该引脚保持为低电平状态。在传输数据时该信号的高电平和低电平的最短保持时间为160 ns,信号的最小周期为400 ns;

- MDIO:用于与PHY之间的数据传输,与MDC时钟线配合,接收/发送数据。

#### 图 2-36. 站点管理接口电路

MAC模块所用引脚在MII/RMII模式下,默认及重映射的功能和具体配置,如<u>表2-12. 以太网信</u> <u>号(MII模式)</u>和表2-13. 以太网信号(RMII模式)</u>所示。

表 2-12. 以太网信号 (MII 模式)

| 信号         | 引脚1  | 引脚2  | 引脚模式(AF11) |

|------------|------|------|------------|

| MDC        | PC1  | •    | 推挽复用输出     |

| MII_TXD2   | PC2  | -    | 推挽复用输出     |

| MII_TX_CLK | PC3  | -    | 浮空输入(复位状态) |

| MII_CRS    | PA0  | PH2  | 浮空输入(复位状态) |

| MII_RX_CLK | PA1  | -    | 浮空输入(复位状态) |

| MDIO       | PA2  | -    | 推挽复用输出     |

| MII_COL    | PA3  | PH3  | 浮空输入(复位状态) |

| MII_RX_DV  | PA7  | -    | 浮空输入(复位状态) |

| MII_RXD0   | PC4  | -    | 浮空输入(复位状态) |

| MII_RXD1   | PC5  | -    | 浮空输入(复位状态) |

| MII_RXD2   | PB0  | PH6  | 浮空输入(复位状态) |

| MII_RXD3   | PB1  | PH7  | 浮空输入(复位状态) |

| PPS_OUT    | PB5  | PG8  | 推挽复用输出     |

| MII_TXD3   | PB8  | PE2  | 推挽复用输出     |

| MII_RX_ER  | PB10 | Pl10 | 浮空输入(复位状态) |

| MII_TX_EN  | PB11 | PG11 | 推挽复用输出     |

| MII_TXD0   | PB12 | PG13 | 推挽复用输出     |

| MII_TXD1   | PB13 | PG14 | 推挽复用输出     |

表 2-13. 以太网信号 (RMII 模式)

| 信号         | 引脚1  | 引脚2  | 引脚模式(AF11) |

|------------|------|------|------------|

| MDC        | PC1  | -    | 推挽复用输出     |

| REF_CLK    | PA1  | -    | 浮空输入(复位状态) |

| MDIO       | PA2  | -    | 推挽复用输出     |

| CRS_DV     | PA7  | -    | 浮空输入(复位状态) |

| RMII_RXD0  | PC4  | -    | 浮空输入(复位状态) |

| RMII_RXD1  | PC5  | -    | 浮空输入(复位状态) |

| PPS_OUT    | PB5  | PG8  | 推挽复用输出     |

| RMII_TX_EN | PB11 | PG11 | 推挽复用输出     |

| 信号        | 引脚1  | 引脚2  | 引脚模式(AF11) |

|-----------|------|------|------------|

| RMII_TXD0 | PB12 | PG13 | 推挽复用输出     |

| RMII_TXD1 | PB13 | PG14 | 推挽复用输出     |

**注意:** 对任意接口模式 (MII / RMII),应用程序都需确保引脚1或引脚2中只有一个被映射到 AF11。

针对GD32F5xx系列产品支持的以太网外设,有如下两种推荐电路供参考。

图 2-37. 媒体独立接口 (MII) 推荐电路

图 2-38. 精简媒体独立接口(RMII)信号线

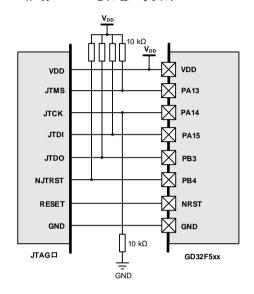

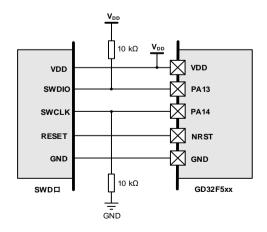

### 2.5. 下载调试电路

GD32F5xx系列内核支持JTAG调试接口与SWD调试接口。JTAG接口标准为20针接口,其中5根信号接口,SWD接口标准为5针接口,其中2根信号接口。

注意:复位后,调试相关端口为输入PU/PD模式,其中:

PA15: JTDI为上拉模式;

PA14: JTCK / SWCLK为下拉模式;

PA13: JTMS / SWDIO为上拉模式;

PB4: NJTRST为上拉模式;

PB3: JTDO为浮空模式。

#### 表 2-14. JTAG 下载调试接口分配

| 备用功能   | GPIO 端口 |

|--------|---------|

| JTMS   | PA13    |

| JTCK   | PA14    |

| JTDI   | PA15    |

| JTDO   | PB3     |

| NJTRST | PB4     |

图 2-39. 推荐 JTAG 接线参考设计

表 2-15. SWD下载调试接口分配

| 备用功能  | GPIO 端口 |

|-------|---------|

| SWDIO | PA13    |

| SWCLK | PA14    |

图 2-40. 推荐 SWD 接线参考设计

有以下几种方式可以提高SWD下载调试通信的可靠性,增强下载调试的抗干扰能力。

- 1. 缩短SWD两个信号线长度,最好15 cm以内;

- 2. 将SWD两根线和GND线编个麻花,缠在一起;

- 3. 在SWD两根信号线对地各并几十pF小电容;

- 4. SWD两根信号线任意IO串入100 Ω ~ 1 kΩ电阻。

## 2.6. 参考原理图设计

#### 图 2-41. GD32F5xx 推荐参考原理图设计

## 3. PCB Layout 设计

为提升MCU功能的稳定性及EMC性能,不仅需要考虑配套外围元器件性能,PCB的Layout也至关重要。另外,在条件允许的情况下,尽量选用有独立GND层和独立电源层的PCB设计方案,这样可以提供更好的EMC性能。如果条件不允许,无法提供独立的GND层和电源层,那也需要保证有一个良好的供电和接地设计,如尽量保持MCU下方GND平面的完整性等。

在有大功率或可产生强干扰的应用下,需要考虑将MCU远离这些强干扰源。

## 3.1. 电源去耦电容

GD32F5xx系列电源有VDD、VDDA、VREFP等供电脚,100 nF去耦电容采用陶瓷MLCC即可,且需要保证位置尽可能地靠近电源引脚。电源走线时,要尽量经过电容后再到达MCU电源引脚,建议可通过靠近电容PAD处打Via的形式Layout。

图 3-1. 推荐电源引脚去耦 Layout 设计

## 3.2. 时钟电路

GD32F5xx系列时钟有HXTAL和LXTAL,要求时钟电路(包括晶体或晶振及电容等)靠近MCU时钟引脚放置,且尽量时钟走线由GND包裹起来。

#### 图 3-2. 推荐时钟引脚 Layout 设计 (无源晶体)

#### 注意:

- 1. 晶体尽量靠近MCU时钟pin, 匹配电容等尽量靠近晶体;

- 2. 整个电路尽量与MCU在同层, 走线尽量不要穿层;

- 3. 时钟器件及走线区域下方的相邻层,尽量禁空,不走任何与时钟无关走线,也不铺铜;

- 4. 大功率、强干扰风险器件及高速走线尽量远离时钟晶体电路;

- 5. 时钟线进行包地处理,以起到屏蔽效果。

## 3.3. 复位电路

NRST引脚走线PCB Layout参考如下:

图 3-3. 推荐 NRST 走线 Layout 设计

**注意**:复位电路阻容等尽可能地靠近MCUNRST引脚,且NRST走线尽量远离强干扰风险器件及高速走线等,条件允许的话,最好将NRST走线做包地处理,以起到更好的屏蔽效果。

### 3.4. USB 电路

对于GD32F5xx系列MCU USB FS模块有DM、DP两根差分信号线,对于USB HS模块,连接外部高速PHY后,PHY芯片也会引出DM、DP两根差分信号线,建议PCB走线要求做特性阻抗90 Ω,差分走线严格按照等长等距规则来走,且尽量使走线最短,如果两条差分线不等长,可在终端用蛇形线补偿短线。由于阻抗匹配考虑,串联匹配电阻建议50 Ω左右即可。

DM、DP差分走线参考如下:

图 3-4. 推荐 DM、DP 差分走线 Layout 设计(1)

图 3-5. 推荐 DM、DP 差分走线 Layout 设计(2)

推荐: R3 = R4 = 50 Ω, R2 = 1 MΩ, C1 = 4700 pF。

#### 注意:

- 1. 布局时摆放合理,以缩短差分走线距离;

- 2. 优先绘制差分线,一对差分线上尽量不要超过两对过孔,且需要对称放置;

- 3. 对称平行走线,保证两根线紧密耦合,避免90°、弧形或45°走线方式;

- 4. 差分走线上所接阻容、EMC等器件,或测试点,也要做到对称原则。

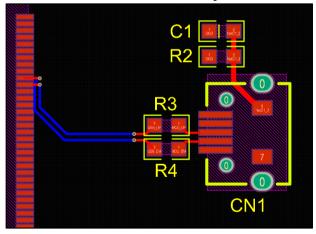

对于USB HS模块,MCU与外部HS PHY之间的数据线与信号控制线也尽量走短,需要用蛇形线做等长处理,参考如下:

#### 图 3-6. 推荐 MCU 与 PHY Layout 设计

#### 注意:

- 1. 图中只绘制了MCU与USB HS-PHY之间的连线,其他电路未绘制;

- 2. 布局时摆放合理, USB HS-PHY芯片与MCU之间尽量紧凑;

- 3. 布线时,以信号线中最长的一根线长度为目标,将其他信号线通过蛇形走线补偿即可。

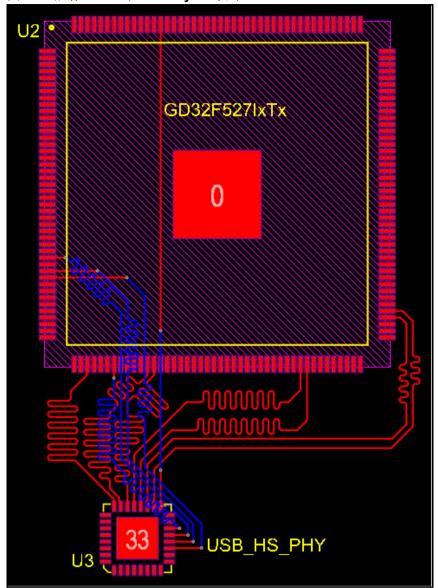

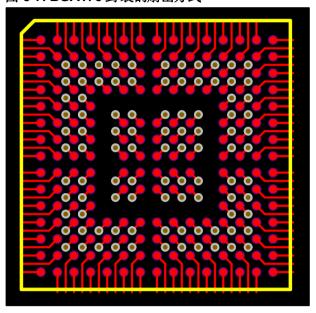

## 3.5. BGA 封装的扇出

对于GD32F5xx系列MCU部分型号存在BGA176(0.65 mmPitch)封装,推荐以下的走线规则与扇出方式。

#### 图 3-7. BGA176 封装的扇出方式

对于0.65 mm Pitch的BGA封装,单个引脚走线不建议大于焊盘直径,即0.25 mm。推荐使用规则设置4 mil线宽线距,使用8/12 mil(若所过电流较大,8/13 mil亦可,大于8/13 mil,4 mil线宽线距无法出线)过孔进行扇出,扇出后如图3-7. BGA176封装的扇出方式所示,过孔距焊盘距离为6.2 mil。

## 4. 钢网与焊接

#### 4.1. 钢网

SMT 贴片时,钢网的厚度和漏孔的开口尺寸,取决于锡膏的种类、焊盘开孔的分布、密度以及间距等因素。钢网漏孔开口尺寸过大,往往导致锡膏分布量过多,容易造成焊接过程中的"桥连"情况。漏洞开口尺寸过小,会导致锡膏使用过少,导致焊点强度不足,或焊点强度不足的"虚焊"。

#### 4.1.1. 钢网推荐厚度

钢网的厚度和开孔尺寸一般遵循规则: 宽厚比高于 1.5 (即钢网的开孔宽度是钢网厚度的 1.5 倍及以上)、面积高于 0.66 (即钢网开孔面积是开孔柱体侧面积的 0.66 倍及以上),这样可以最大程度保证刷锡时,在焊盘上有适当量的锡膏。

GD32F5xx 系列新品推荐钢网厚度如表 4-1. GD32F5xx 芯片推荐钢网厚度所示。

表 4-1. GD32F5xx 芯片推荐钢网厚度

| 芯片封装                     | 厚度(mm) |

|--------------------------|--------|

| LQFP176(24x24, 0.5pitch) | 0.12   |

| BGA176(10x10, 0.65pitch) | 0.12   |

| LQFP144(20x20, 0.5pitch) | 0.12   |

| LQFP100(14x14, 0.5pitch) | 0.12   |

| LQFP64(10x10, 0.5pitch)  | 0.12   |

在具体实践中,上表仅可作为 GD32F5xx 系列产品钢网厚度参考,具体电路板钢网厚度,请结合电路板上器件密度、其他芯片引脚 pitch 值和焊盘尺寸及工艺要求,综合评估。

#### 4.1.2. 钢网的清洁与使用

#### 钢网的清洁

- 使用前应该先清洗钢网,以除去运输过程或长期放置中沾染到的污染物;

- 钢网使用完后应及时清洗干净,装回包装,放置在专用储藏位置;

- 对于等待清洗的钢网,不可随意放置,避免损坏钢网,或者引入其他污染物;

- 钢网应该竖直放置在专用储藏位置,钢网之间应相互隔离,禁止叠放或相互接触。

#### 钢网的使用

- 用来焊接的锡膏应升温和搅拌均匀后使用, 避免堵塞钢网:

- 移动钢网时应轻拿轻放,避免钢网磕碰到硬物或锋利器具;

- 刷锡时钢网应紧贴电路板,且注意调整刮刀上的压力,以钢网上不留残余锡膏同时不伤 害钢网为宜:

- 刷锡后,停顿3 s左右,再抬起钢网脱模,脱模速度不宜过快;

- 一般钢网使用寿命为10万次,达到使用寿命极限的钢网应报废,禁止钢网超额使用。

## 4.2. 焊接

在实际加工生产过程中,回流焊炉温曲线设置需要参考很多因素,除了元器件自身特性外,还需要考虑如印刷电路板材质、元器件分布密度、锡膏成分等因素。下面给大家介绍针对GD32F5xx系列芯片的回流焊炉温曲线,供参考。

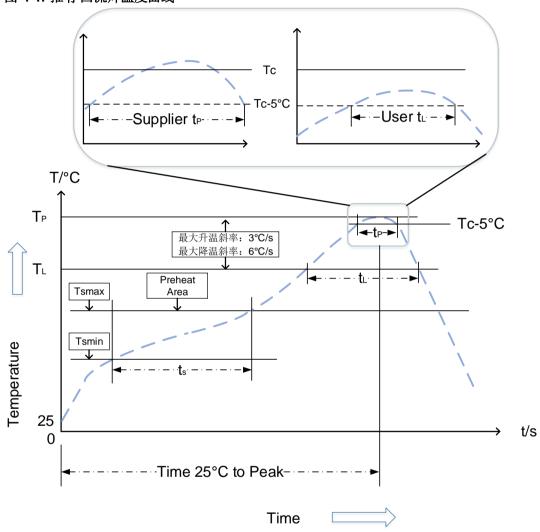

图 4-1. 推荐回流焊温度曲线

表 4-2. 回流焊相关参数

| 特征参数                      | 无铅装配          |

|---------------------------|---------------|

| 平均升温斜率(217 ℃到峰值温度)        | 最大 3 ℃ /s     |

| 预热 (150 °C - 200 °C) 持续时间 | 60 – 120 s    |

| 保持 217 ℃ 以上的时间            | 60 – 150 s    |

| 峰值温度                      | 260 + 5/-0 °C |

| 真实峰值温度 5 °C 以内持续时间        | 30 s          |

| 降温斜率                      | 最大 6 ℃ /s     |

| 从 25 °C 到温度峰值时间           | 最大 8 min      |

## 5. 封装说明

GD32F5xx系列共有6种封装形式,分别为BGA176、LQFP176、LQFP144、LQFP100和LQFP64。

表 5-1. 封装型号说明

| 200 2000      |                          |

|---------------|--------------------------|

| 产品型号          | 封装                       |

| GD32F527lxK6  | BGA176(10x10, 0.65pitch) |

| GD32F527lxTx  | LQFP176(24x24, 0.5pitch) |

| GD32F527ZxT6  | LQFP144(20x20, 0.5pitch) |

| GD32F527VxT6  | LQFP100(14x14, 0.5pitch) |

| GD32F527Rx T6 | LQFP64(10x10, 0.5pitch)  |

(尺寸单位为毫米mm)

## 6. 版本历史

表 6-1. 版本历史

| 版本号. | 说明   | 日期          |

|------|------|-------------|

| 1.0  | 首次发布 | 2023年12月20日 |

#### **Important Notice**

This document is the property of GigaDevice Semiconductor Inc. and its subsidiaries (the "Company"). This document, including any product of the Company described in this document (the "Product"), is owned by the Company under the intellectual property laws and treaties of the People's Republic of China and other jurisdictions worldwide. The Company reserves all rights under such laws and treaties and does not grant any license under its patents, copyrights, trademarks, or other intellectual property rights. The names and brands of third party referred thereto (if any) are the property of their respective owner and referred to for identification purposes only.

The Company makes no warranty of any kind, express or implied, with regard to this document or any Product, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. The Company does not assume any liability arising out of the application or use of any Product described in this document. Any information provided in this document is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Except for customized products which has been expressly identified in the applicable agreement, the Products are designed, developed, and/or manufactured for ordinary business, industrial, personal, and/or household applications only. The Products are not designed, intended, or authorized for use as components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, atomic energy control instruments, combustion control instruments, airplane or spaceship instruments, transportation instruments, traffic signal in struments life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or Product could cause personal injury, death, property or environmental damage ("Unintended Uses"). Customers shall take any and all actions to ensure using and selling the Products in accordance with the applicable laws and regulations. The Company is not liable, in whole or in part, and customers shall and hereby do release the Company as well as it's suppliers and/or distributors from any claim, damage, or other liability arising from or related to all Unintended Uses of the Products. Customers shall indemnify and hold the Company as well as it's suppliers and/or distributors harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of the Products.

Information in this document is provided solely in connection with the Products. The Company reserves the right to make changes, corrections, modifications or improvements to this document and Products and services described herein at any time, without notice.

© 2023 GigaDevice - All rights reserved