# GigaDevice Semiconductor Inc.

# GDSCN832xx

## **User Manual**

Revision 1.0

(Apr. 2024)

# **Table of Contents**

| Table   | of Contents                                                   | 2  |

|---------|---------------------------------------------------------------|----|

| List of | f Figures                                                     | 9  |

| List of | f Tables                                                      | 11 |

|         | System and bus architecture                                   |    |

| 1.1.    | Bus architecture                                              |    |

|         |                                                               |    |

| 1.2.    | Memory map                                                    |    |

| 1.3.    | AHB direct/indirect access                                    |    |

| 1.3     | 3                                                             |    |

| 1.3     | ÿ                                                             |    |

| 1.3     | 3.3. Indirect transmit access ESC core PRAM                   | 16 |

| 1.4.    | Register protection in BUSY state                             | 17 |

| 1.5.    | OPB transmission timeout function                             | 18 |

| 1.6.    | EFUSE function                                                | 18 |

| 1.7.    | EFUSE Register definition                                     | 19 |

| 1.7     | · · · · · · · · · · · · · · · · · · ·                         |    |

| 1.7     | 7.2. EFUSE UID READ register (EFUSE_UID_READ)                 |    |

| 1.8.    | ESC core controller (ESC_CCTL)                                | 20 |

| 1.9.    | ESC core controller register definition                       | 20 |

| 1.9     | 0.1. ESC CCTL data register (ESC_CCTL_DATA)                   | 20 |

| 1.9     | 0.2. ESC CCTL command register (ESC_CCTL_CMD)                 | 21 |

| 1.9     | 0.3. ESC PRAM FIFO data read register (ESC_PRAM_FIFO_DR)      | 21 |

| 1.9     | 0.4. ESC PRAM address and length read register (ESC_PRAM_ALR) | 22 |

| 1.9     | 9.5. ESC PRAM command read register (ESC_PRAM_CR)             | 22 |

| 1.9     | 3 \ = = = ,                                                   |    |

| 1.9     |                                                               |    |

| 1.9     |                                                               |    |

| 1.9     | 9.9. ESC OPB control and status register (ESC_OPB_CS)         | 25 |

| 1.10.   | System configuration controller (SYSCFG)                      | 27 |

| 1.11.   | System configuration register definition                      | 27 |

| 1.1     | 1.1. System configuration register 0 (SYSCFG_CFG0)            |    |

| 1.1     | 1.2. SYSCFG chip id register (SYSCFG_CHIPID)                  |    |

| 1.1     | 1.3. SYSCFG chip version register (SYSCFG_CHIPVER)            |    |

| 1.1     | 1.4. SYSCFG reserved register (SYSCFG_RESERVED)               | 28 |

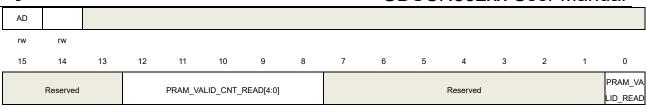

| 2. F    | Power management unit (PMU)                                   | 30 |

| _     | OBCOTTOCZAX CCCT                                                   | Manaai |

|-------|--------------------------------------------------------------------|--------|

| 2.1.  | Overview                                                           | 30     |

| 2.2.  | Characteristics                                                    | 30     |

| 2.3.  | Function overview                                                  | 30     |

| 2.3.  | 1. Device ready                                                    | 30     |

| 2.3.2 | 2. EFUSE voltage supply                                            | 31     |

| 2.3.3 | 3. PHY wake up event detection                                     | 31     |

| 2.3.4 | 4. PME wake up notification                                        | 31     |

| 2.3.  | 5. Module level power saving modes                                 | 31     |

| 2.3.6 | 6. Device level power saving modes                                 | 32     |

| 2.3.7 | 7. Entering device level power saving modes                        | 33     |

| 2.3.8 | B. Exiting device level power saving modes                         | 33     |

| 2.4.  | Register definition                                                | 35     |

| 2.4.  | 1. Control register 0 (PMU_CTL0)                                   | 35     |

| 2.4.2 | 2. Control and status register (PMU_CTL1)                          | 37     |

| 2.4.3 | 3. Process data interface reference value register (PMU_PDIREFVAL) | 37     |

| 3. R  | eset and clock unit (RCU)                                          | 39     |

| 3.1.  | Reset control unit (RCTL)                                          | 39     |

| 3.1.  | • •                                                                |        |

| 3.1.2 | 2. Characteristics                                                 | 39     |

| 3.1.3 | 3. Function overview                                               | 39     |

| 3.2.  | Clock control unit (CCTL)                                          | 40     |

| 3.2.  | ,                                                                  |        |

| 3.2.2 |                                                                    |        |

| 3.2.3 |                                                                    |        |

| 3.3.  | Register definition                                                | 42     |

|       | 1. AHB enable register (RCU_AHBEN)                                 |        |

| 3.3.2 |                                                                    |        |

| 3.3.3 | 3. Core enable register (RCU_COREEN)                               | 44     |

| 3.3.4 | 4. Clock configuration register (RCU_CLKCFG)                       | 45     |

| 3.3.  | 5. Reset configuration register (RCU_RSTCFG)                       | 46     |

| 3.3.6 | 6. PLL configuration key register (RCU_PLL_CFG_KEY)                | 47     |

| 3.3.7 |                                                                    |        |

| 4. Ir | nterrupt controller (INTC)                                         | 49     |

| 4.1.  | Overview                                                           |        |

| 4.2.  | Characteristics                                                    | 49     |

| 4.3.  | Interrupts function overview                                       | 49     |

| 4.3.  | •                                                                  |        |

| 4.3.2 | 2. Device ready interrupt                                          | 50     |

| 4.3.3 | 3. Ethernet PHY interrupt                                          | 50     |

|       |                                                                    |        |

| 4.3.4.               | Timer interrupt                                                | 51 |

|----------------------|----------------------------------------------------------------|----|

| 4.3.5.               | PME interrupt                                                  | 51 |

| 4.3.6.               | AHB2OPB bridge interrupt                                       | 51 |

| 4.3.7.               | EtherCAT interrupt                                             | 51 |

| 4.3.8.               | Clock output test mode                                         | 52 |

| 4.4. R               | Register definition                                            | 52 |

| 4.4.1.               | Control register (INTC_CTL)                                    | 52 |

| 4.4.2.               | Flag register (INTC_FLAG)                                      | 53 |

| 4.4.3.               | Enable register (INTC_EN)                                      | 55 |

| 5. Gei               | neral-purpose I/Os (GPIO)                                      | 57 |

| 5.1. O               | Overview                                                       | 57 |

| 5.2. C               | Characteristics                                                | 57 |

|                      | unction overview                                               |    |

| 5.3.1.               | GPIO pin configuration                                         |    |

| 5.3.2.               | External interrupt/event lines                                 |    |

| 5.3.3.               | Alternate functions (AF)                                       |    |

| 5.3.4.               | . ,                                                            |    |

| 5.3.5.               | Alternate function (AF) configuration                          |    |

|                      | · , ·                                                          |    |

| <b>5.4. R</b> 5.4.1. | Register definition  Port output mode register0 (GPIO0_OMODE0) |    |

| 5.4.1.<br>5.4.2.     | ·                                                              |    |

| 5.4.2.               |                                                                |    |

| 5.4.3.<br>5.4.4.     |                                                                |    |

| 5.4.4.<br>5.4.5.     | · · · · · · · · · · · · · · · · · · ·                          |    |

| 5.4.6.               | Port pull-up/down register (GPIO0_PUD1)                        |    |

| 5.4.7.               |                                                                |    |

| 5.4.8.               | Port pull-up/down register3 (GPIO1_PUD1)                       |    |

| 5.4.9.               | EXMC control register (EXMC_CTL)                               |    |

|                      | • · · - ·                                                      |    |

|                      | /IER                                                           |    |

|                      | Basic Timer                                                    |    |

| 6.1.1.               | Overview                                                       |    |

| 6.1.2.               | Characteristics                                                |    |

| 6.1.3.               | Block diagram                                                  |    |

| 6.1.4.               |                                                                |    |

| 6.1.5.               | Registers definition                                           | 72 |

| 6.2. F               | ree-Running Counter (FRC)                                      |    |

| 6.2.1.               | Overview                                                       |    |

| 6.2.2.               | Characteristics                                                |    |

| 6.2.3.               | Block diagram                                                  | 74 |

| 6.2.4.               | Function overview                                              | 74 |

|         | 0200110                                       |     |

|---------|-----------------------------------------------|-----|

| 6.2.5.  | Registers definition                          | 75  |

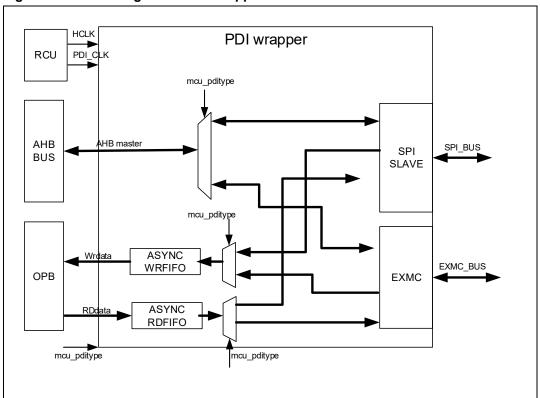

| 7. PDI  | Wrapper                                       | 76  |

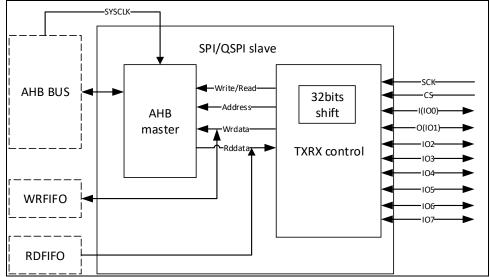

| 7.1. SI | PI/QSPI/OSPI slave                            | 77  |

| 7.1.1.  | Overview                                      | 77  |

| 7.1.2.  | Characteristics                               | 77  |

| 7.1.3.  | Block diagram                                 | 77  |

| 7.1.4.  | SPI signal description                        | 77  |

| 7.1.5.  | SPI/QSPI/OSPI slave controller                | 79  |

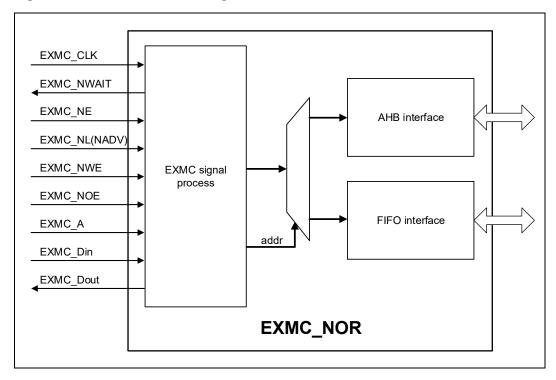

| 7.2. Ex | xternal memory controller (EXMC)              | 99  |

| 7.2.1.  | Overview                                      |     |

| 7.2.2.  | Characteristics                               |     |

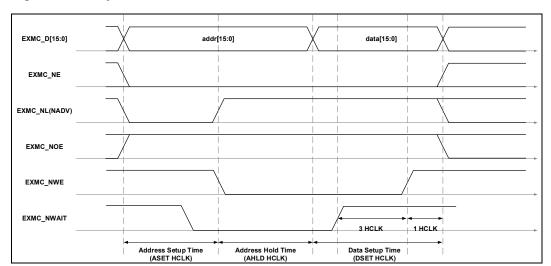

| 7.2.3.  | Function overview                             | 99  |

| 8. Eth  | ernet PHYS                                    | 105 |

| 8.1. O  | verview                                       | 105 |

| 8.2. CI | haracteristics                                | 105 |

| 8.3. Fu | unctional Overview                            | 106 |

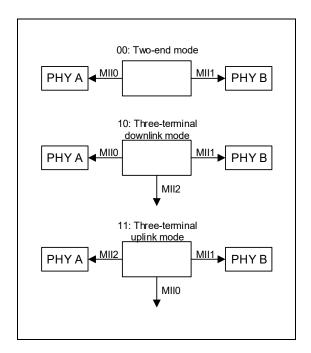

| 8.3.1.  | Operation Mode                                | 106 |

| 8.3.2.  | MII Interface                                 | 106 |

| 8.3.3.  | SMI Interface                                 | 107 |

| 8.3.4.  | Automatic MDI/MDIX and Polarity Configuration | 107 |

| 8.3.5.  | Loopback Modes                                | 107 |

| 8.3.6.  | Wake-On-LAN                                   | 107 |

| 8.3.7.  | LED Modes                                     | 107 |

| 8.3.8.  | LPI Signaling                                 | 108 |

| 8.4. PI | HY Register definition                        | 109 |

| 8.4.1.  | Page 0 Registers                              | 109 |

| 8.4.2.  | Page 1 Registers                              | 127 |

| 8.4.3.  | Page 2 Registers                              | 127 |

| 8.4.4.  | Page 3 Registers                              | 129 |

| 8.4.5.  | Page 6 Registers                              | 130 |

| 8.4.6.  | Page 9 Registers                              |     |

| 8.4.7.  | MDIO Registers                                | 138 |

| 9. Eth  | erCAT                                         | 155 |

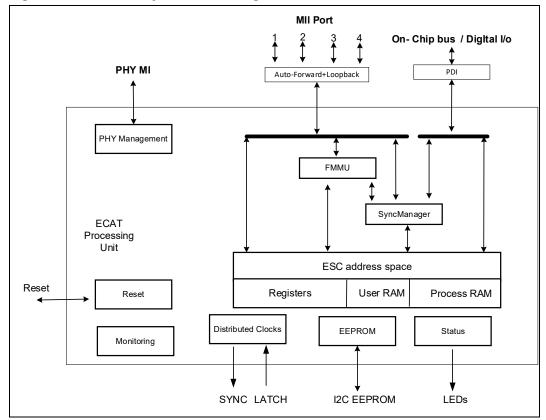

| 9.1. O  | verview                                       | 155 |

| 9.2. CI | haracteristics                                | 155 |

| 9.2.1.  | Block diagram                                 |     |

| 9.2.2.  | EtherCAT SubDevice Controller Function Blocks | 156 |

| 9.3. Fu | unction overview                              | 158 |

| 9.3.1.  | Process Data Interface (PDI)                                  | 158 |

|---------|---------------------------------------------------------------|-----|

| 9.3.2.  | FMMU                                                          | 160 |

| 9.3.3.  | SyncManager                                                   | 161 |

| 9.3.4.  | Distributed Clocks                                            | 162 |

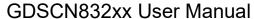

| 9.3.5.  | EtherCAT State Machine                                        | 162 |

| 9.3.6.  | EEPROM                                                        | 163 |

| 9.3.7.  | RESET                                                         | 164 |

| 9.3.8.  | Interrupts                                                    | 164 |

| 9.3.9.  | LED                                                           | 166 |

| 9.4. ES | SC Register definition                                        | 166 |

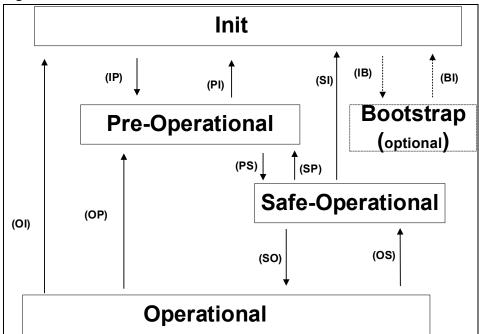

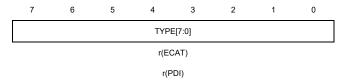

| 9.4.1.  | ESC Type register (ESC_TYPE)                                  |     |

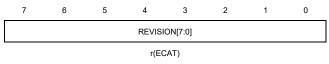

| 9.4.2.  | ESC Revision register (ESC_REVISION)                          | 167 |

| 9.4.3.  | ESC Build register (ESC_BUILD)                                | 167 |

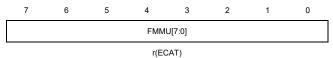

| 9.4.4.  | ESC FMMU Numbers register (ESC_FMMUS)                         | 167 |

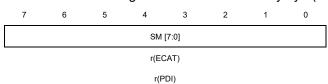

| 9.4.5.  | ESC SyncManagers Numbers register (ESC_SYNCMANAGERS)          | 168 |

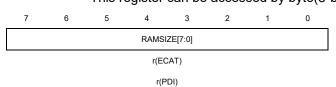

| 9.4.6.  | ESC RAM size register (ESC_RAMSIZE)                           | 168 |

| 9.4.7.  | ESC Port Descriptor register (ESC_PORT_DESCRIPTION)           | 168 |

| 9.4.8.  | ESC Features supporter register (ESC_FEATURES_SUPPORTED)      |     |

| 9.4.9.  | ESC Configured station address register (ESC_STATION_ADDRESS) | 171 |

| 9.4.10. | ESC Configured station Alias register (ESC_STATION_ALIAS)     | 171 |

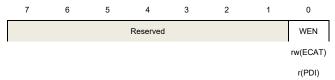

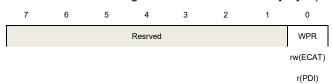

| 9.4.11. | Write Enable register (WRITE_ENABLE)                          | 171 |

| 9.4.12. | ESC Write Protection register (ESC_WRITE_PROTECTION)          | 172 |

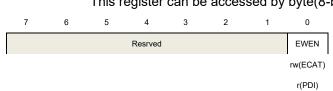

| 9.4.13. | ESC Write Enable register (ESC_ WRITE_ENABLE)                 |     |

| 9.4.14. | ESC Write Protection register (ESC_WRITE_PROTECTION)          | 173 |

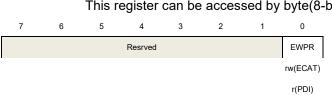

| 9.4.15. | ESC Reset register (ESC_RESET_ECAT)                           | 173 |

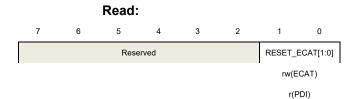

| 9.4.16. | ESC Reset PDI register (ESC_RESET_PDI)                        | 174 |

| 9.4.17. | ESC DL Control register (ESC_DL_CONTROL)                      | 175 |

| 9.4.18. | ESC Physical read/write offset register (ESC_PHYSICAL_OFFSET) | 177 |

| 9.4.19. | ESC DL Status register (ESC_DL_STATUS)                        | 177 |

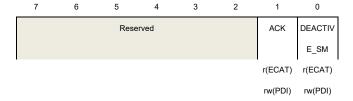

| 9.4.20. | ESC AL Control register (ESC_AL_CONTROL)                      | 179 |

| 9.4.21. | ESC AL Status register (ESC_AL_STATUS)                        | 180 |

| 9.4.22. | ESC AL Status Code register (ESC_AL_STATUS_CODE)              | 181 |

| 9.4.23. | ESC RUN LED Override register (ESC_RUN_LED)                   | 181 |

| 9.4.24. | ESC ERR LED Override register (ESC_ERR_LED)                   | 182 |

| 9.4.25. | ESC PDI Control register (ESC_PDI_CONTROL)                    | 182 |

| 9.4.26. | ESC Configuration register (ESC_CONFIG)                       | 183 |

| 9.4.27. | ESC PDI Information register (ESC_PDI_INFM)                   | 184 |

| 9.4.28. | ESC PDI configuration register (ESC_PDI_CONFIG)               | 184 |

| 9.4.29. | ESC Sync/Latch configuration register (ESC_SL_CONFIG)         | 185 |

| 9.4.30. | ESC PDI extended configuration register (ESC_DEXT_CFG)        | 186 |

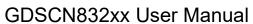

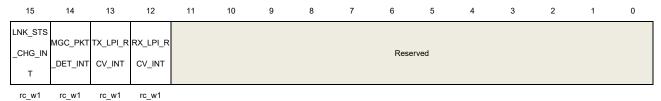

| 9.4.31. | ESC Event Mask register (ESC_EVENT_MASK)                      | 188 |

| 9.4.32. | ESC PDI AL Event register (ESC_PDI_AL_EVENT)                  | 188 |

| 9.4.33. | ESC Event Request register (ESC_EVENT_RQST)                   | 189 |

| _ |         | OBCONOCEXX Cool Mand                                                                  | <i>1</i> 41 |

|---|---------|---------------------------------------------------------------------------------------|-------------|

|   | 9.4.34. | ESC AL Event Request register (ESC_AL_EVENT_RQST)                                     | 190         |

|   | 9.4.35. | RX Error Port X register (RX_PORTX_ERROR) (X = 0,1,2,3)                               | 193         |

|   | 9.4.36. | Forwarded RX Error Port X register (FRX_PORTX_ERROR) (X = 0,1,2,3)                    |             |

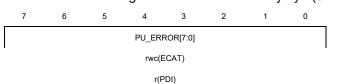

|   | 9.4.37. | ESC Processing Unit Error register (ESC_PU_ERROR)                                     | 194         |

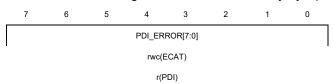

|   | 9.4.38. | ESC PDI Error Counter register (ESC_PDI_ERROR)                                        | 194         |

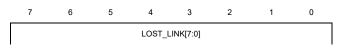

|   | 9.4.39. | ESC PORT X Lost Link register (ESC_PORTX_LOST_LINK) (X = 0,1,2,3)                     | 194         |

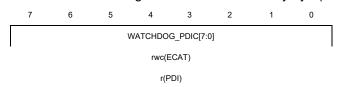

|   | 9.4.40. | ESC Watchdog Divider register (ESC_WTG_DIVIDER)                                       | 195         |

|   | 9.4.41. | ESC Watchdog Time PDI register (ESC_WTG_TIME)                                         | 195         |

|   | 9.4.42. | ESC Watchdog Time Process Data register (ESC_WTG_TPD)                                 | 196         |

|   | 9.4.43. | ESC Watchdog Status Process Data register (ESC_WTG_STATUS)                            | 196         |

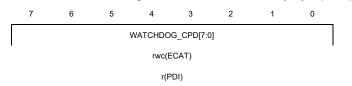

|   | 9.4.44. | ESC Watchdog Counter Process Data register (ESC_WTG_CTR)                              | 196         |

|   | 9.4.45. | ESC Watchdog Counter PDI register (ESC_WTG_CTR_PDI)                                   | 197         |

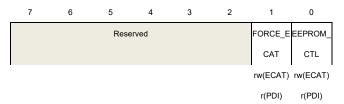

|   | 9.4.46. | ESC EEPOM Configuration register (ESC_EEPROM_CONFIG)                                  | 197         |

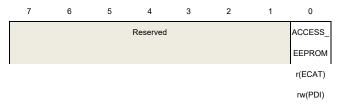

|   | 9.4.47. | ESC EEPOM PDI Access register (ESC_EEPROM_ACCESS)                                     | 198         |

|   | 9.4.48. | ESC EEPOM Contorl/Status register (ESC_EEPROM_CONTROL)                                | 198         |

|   | 9.4.49. | ESC EEPROM Address register (ESC_EEPROM_ADDR)                                         | 200         |

|   | 9.4.50. | ESC EEPROM Data register (ESC_EEPROM_DATA)                                            | 201         |

|   | 9.4.51. | ESC MII Management Control / Status register (ESC_MII_CTL)                            | 201         |

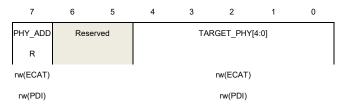

|   | 9.4.52. | ESC PHY Address register (ESC_PHY_ADDR)                                               | 202         |

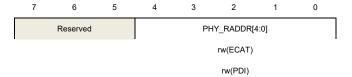

|   | 9.4.53. | ESC PHY Register Address register (ESC_PHY_RADDR)                                     | 203         |

|   | 9.4.54. | ESC PHY Data register (ESC_PHY_DATA)                                                  | 204         |

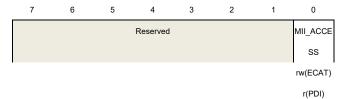

|   | 9.4.55. | MII Management ECAT Access State register (MII_ECAT_STATE)                            | 204         |

|   | 9.4.56. | MII Management ECAT Access State register (MII_PDI_STATE)                             | 204         |

|   | 9.4.57. | PHY Port X Status register (PHY_PORTX_STA) (X = 0,1,2,3)                              | 205         |

|   | 9.4.58. | Logical Start address FMMU X register (FMMUX_LOGIC_ADDR) (X = 0···F)                  | 206         |

|   | 9.4.59. | Length FMMU X register (FMMUX_LENGTH) (X = 0···F)                                     | 206         |

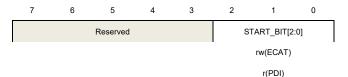

|   | 9.4.60. | Start bit FMMU X in Logical address space register (FMMUX_STRA_BIT) (X = $0\cdots$ F) | 207         |

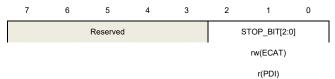

|   | 9.4.61. | Stop bit FMMU X in Logical address space register (FMMUX_STOP_BIT) (X = $0\cdots F$ ) | 207         |

|   | 9.4.62. | Physical Start address FMMU X register (FMMUX_ADRR) (X = 0···F)                       | 207         |

|   | 9.4.63. | Physical Start bit FMMU X register (FMMUX_PSBIT) (X = 0···F)                          | 208         |

|   | 9.4.64. | Type FMMU X register (FMMUX_TYPE) (X = 0···F)                                         |             |

|   | 9.4.65. | Active FMMU X register (FMMUX_ACTIVE) (X = 0···F)                                     | 209         |

|   | 9.4.66. | Physical Start address SyncManager X register (SMX_ADRR) (X = 0···F)                  | 209         |

|   | 9.4.67. | Length SyncManager X register (SMX_LENGTH) (X = 0···F)                                | 209         |

|   | 9.4.68. | Control Register SyncManager X register (SMX_CTL) (X = 0···F)                         | 210         |

|   | 9.4.69. | Status Register SyncManager X register (SMX_STA) (X = 0···F)                          | .211        |

|   | 9.4.70. | Activate SyncManager X register (SMX_ACTIVE) (X = 0···F)                              |             |

|   | 9.4.71. | PDI Control SyncManager X register (SMX_PDICTL) (X = 0···F)                           | 212         |

|   | 9.4.72. | ESC Receive Time Port 0 register (ESC_RECVE_TIMEP0)                                   |             |

|   | 9.4.73. | ESC Receive Time Port 1 register (ESC_RECVE_TIMEP1)                                   |             |

|   | 9.4.74. | ESC Receive Time Port 2 register (ESC_RECVE_TIMEP2)                                   | 214         |

|   | 9.4.75. | ESC System Time register (ESC_SYS_TIME)                                               |             |

|   | 9.4.76. | ESC Receive Time ECAT Processing Unit register (ESC RCVTIME)                          | 215         |

| 9.4.77.  | ESC System Time Offset register (ESC_OFFSET_TIME)                | 215 |

|----------|------------------------------------------------------------------|-----|

| 9.4.78.  | ESC System Time Delay register (ESC_DELAY_TIME)                  | 216 |

| 9.4.79.  | ESC System Time Difference register (ESC_DIFF_TIME)              | 216 |

| 9.4.80.  | ESC Speed Counter Start register (ESC_COUNT_START)               |     |

| 9.4.81.  | ESC Speed Counter Diff register (ESC_COUNT_DIFF)                 | 217 |

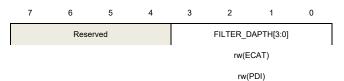

| 9.4.82.  | ESC System Time Difference Filter Depth register (ESC_TIME_DIFF) | 218 |

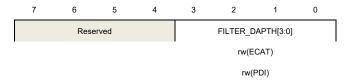

| 9.4.83.  | ESC Speed Counter Filter Depth register (ESC_SPEED_COUNT)        | 218 |

| 9.4.84.  | ESC Cyclic Unit Control register (ESC_UNIT_CTL)                  | 219 |

| 9.4.85.  | ESC Register Activation register (ESC_REGISTER_ACTIVE)           | 219 |

| 9.4.86.  | ESC Pulse Length of SyncSignals register (ESC_PLEN_SM)           | 221 |

| 9.4.87.  | ESC Activation Status register (ESC_ACTIVE_STATUS)               | 221 |

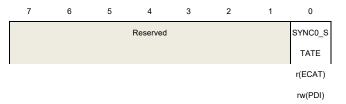

| 9.4.88.  | ESC SYNC0 Status register (ESC_SYNC0_STATUS)                     | 222 |

| 9.4.89.  | ESC SYNC1 Status register (ESC_SYNC1_STATUS)                     | 222 |

| 9.4.90.  | ESC Start Time Cyclic Operation register (ESC_START_TIME)        | 223 |

| 9.4.91.  | ESC Next SYNC1 Pulse register (ESC_NEXT_SYNC1)                   | 223 |

| 9.4.92.  | ESC SYNC0 Cycle Time register (ESC_SYNC0_CYCLE)                  | 223 |

| 9.4.93.  | ESC SYNC1 Cycle Time register (ESC_SYNC1_CYCLE)                  | 224 |

| 9.4.94.  | ESC Latch0 Control register (ESC_LATCH0_CTL)                     | 224 |

| 9.4.95.  | ESC Latch1 Control register (ESC_LATCH1_CTL)                     | 225 |

| 9.4.96.  | ESC Latch0 Status register (ESC_LATCH0_STATUS)                   | 226 |

| 9.4.97.  | ESC Latch1 Status register (ESC_LATCH1_STATUS)                   | 226 |

| 9.4.98.  | ESC Latch0 Time Positive Edge (ESC_LATCH0_POSITIVE)              | 227 |

| 9.4.99.  | ESC Latch0 Time Negative Edge (ESC_LATCH0_NEGATIVE)              | 227 |

| 9.4.100. | ESC Latch1 Time Positive Edge (ESC_LATCH1_POSITIVE)              | 228 |

| 9.4.101. | ESC Latch1 Time Negative Edge (ESC_LATCH1_NEGATIVE)              | 229 |

| 9.4.102. | ESC Buffer Change Event Time register (ESC_EVENT_TIME)           | 229 |

| 9.4.103. | ESC PDI Buffer Start Event Time register (ESC_PDI_SEVENT_TIME)   | 230 |

| 9.4.104. | ESC PDI Buffer Change Event Time register (ESC_PDI_CEVENT_TIME)  | 230 |

| 9.4.105. | ESC Product ID register (ESC_PRODUCT_ID)                         | 231 |

| 9.4.106. | ESC Vendor ID register (ESC_VENDOR_ID)                           | 231 |

|          | ESC Digital I/O Output Data register (ESC_DIG_DATA)              |     |

| 9.4.108. | ESC General Purpose Outputs register (ESC_GP_OUTPUT)             | 232 |

| 9.4.109. | ESC General Purpose Inputs register (ESC_GP_INPUTS)              | 232 |

| 9.4.110. | ESC User RAM register (ESC_USER_RAM)                             | 233 |

| 9.4.111. | ESC PDI Digital I/O Input Data register (ESC_PDI_DATA)           | 233 |

| 9.4.112. | ESC Process Data RAM register (ESC_PDRAM)                        | 233 |

| David    | sion history                                                     | 225 |

# **List of Figures**

| Figure 1-1. Bus architecture of ESC                             | . 12 |

|-----------------------------------------------------------------|------|

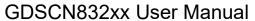

| Figure 1-3 Efuse controller block diagram                       | . 19 |

| Figure 2-1. PME interrupt pending                               | . 31 |

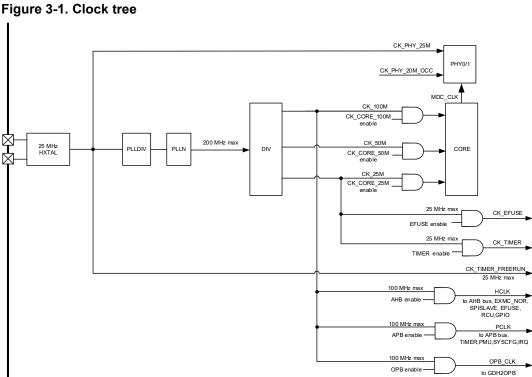

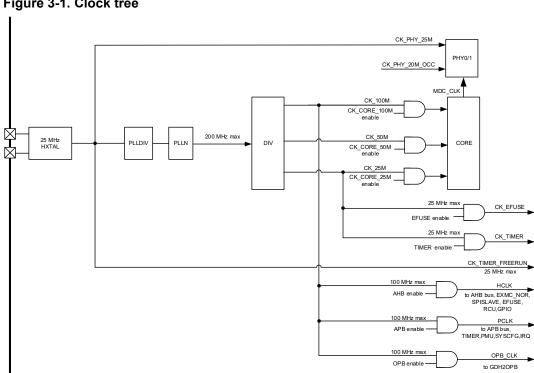

| Figure 3-1. Clock tree                                          | . 41 |

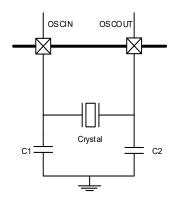

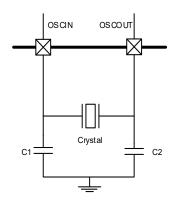

| Figure 3-2. HXTAL clock source                                  | . 42 |

| Figure 4-1. Block diagram of interrupt                          | . 50 |

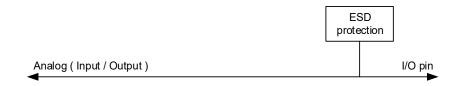

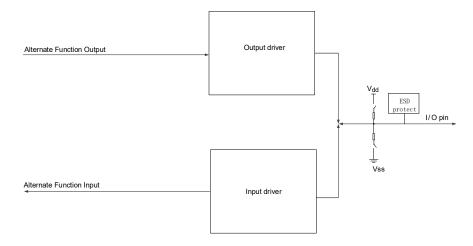

| Figure 5-1. Port line PHYS                                      |      |

| Figure 5-2. Basic structure of Analog configuration             | . 60 |

| Figure 5-3. Basic structure of Alternate function configuration | . 61 |

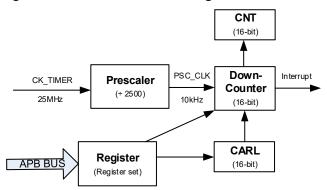

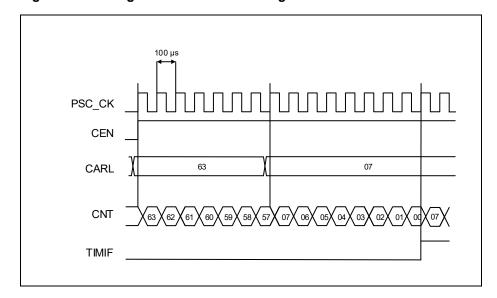

| Figure 6-1. Basic timer block diagram                           | . 71 |

| Figure 6-2. Timing chart of down counting mode                  | . 72 |

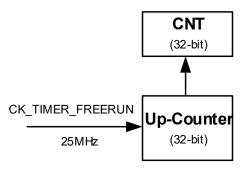

| Figure 6-3. FRC block diagram                                   |      |

| Figure 7-1. Block diagram of PDI wrapper                        |      |

| Figure 7-2. Block diagram of SPI                                | . 77 |

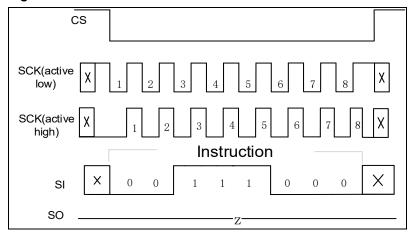

| Figure 7-3. Enable QSPI                                         |      |

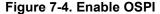

| Figure 7-4. Enable OSPI                                         |      |

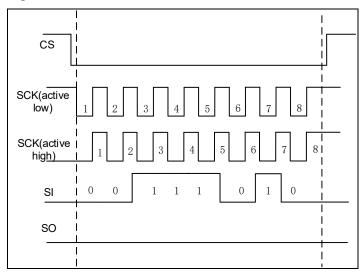

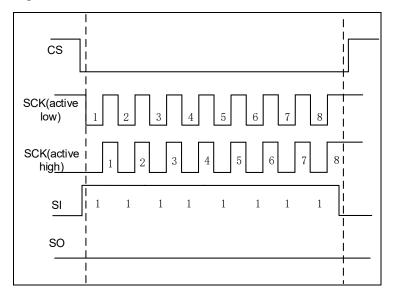

| Figure 7-5. SPI MODE RESET SPI                                  |      |

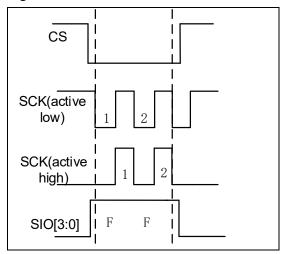

| Figure 7-6. QSPI MODE RESET QSPI                                |      |

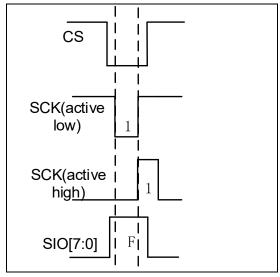

| Figure 7-7. OSPI MODE RESET OSPI                                |      |

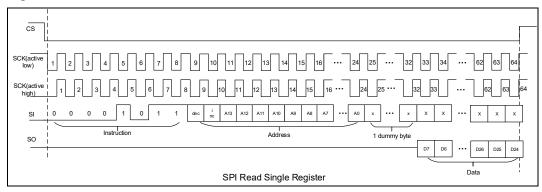

| Figure 7-8. SPI READ                                            |      |

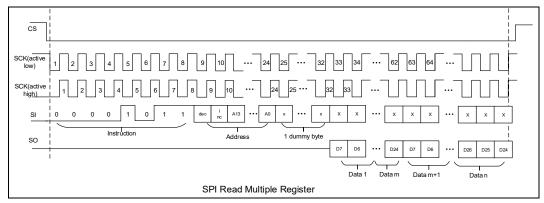

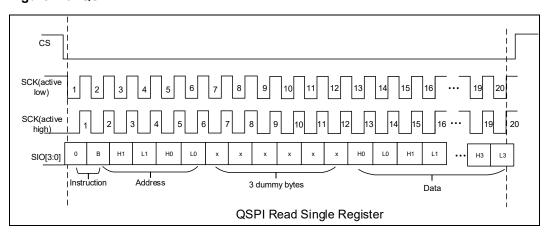

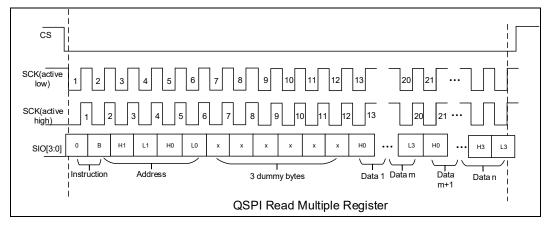

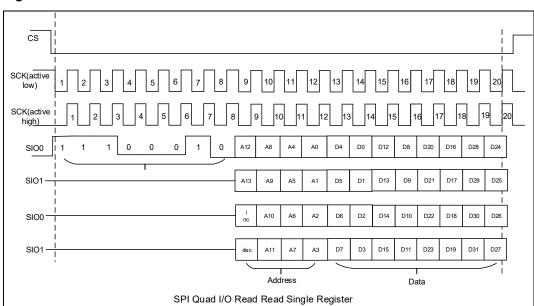

| Figure 7-9. QSPI READ                                           | . 86 |

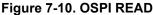

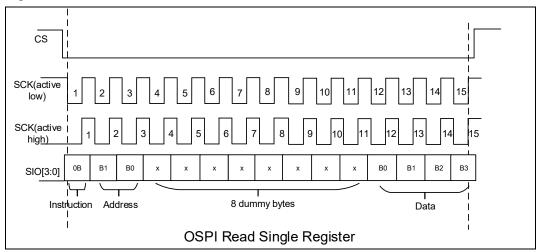

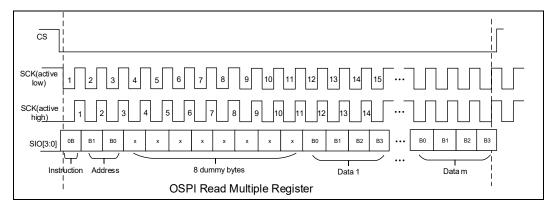

| Figure 7-10. OSPI READ                                          |      |

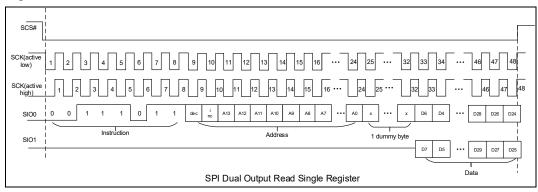

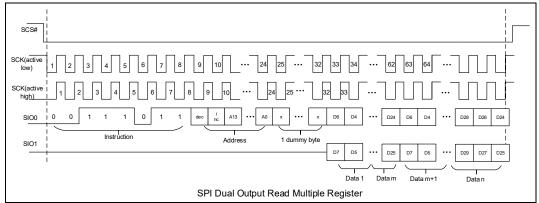

| Figure 7-11. SPI DUAL OUTPUT READ                               |      |

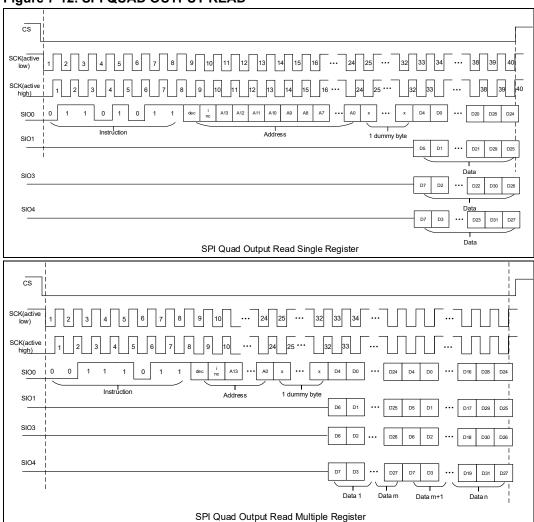

| Figure 7-12. SPI QUAD OUTPUT READ                               |      |

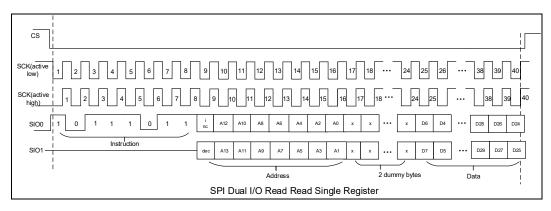

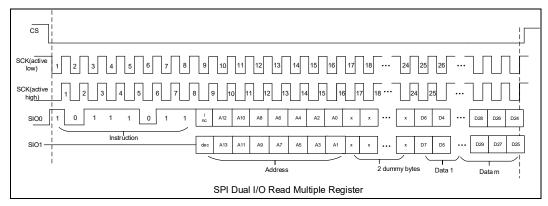

| Figure 7-13. SPI DUAL I/O READ                                  |      |

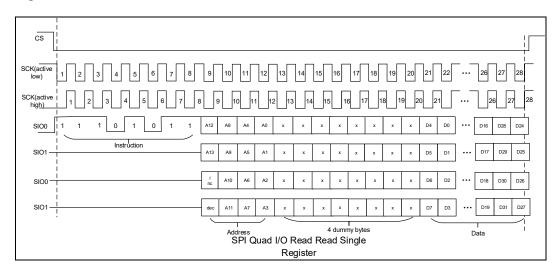

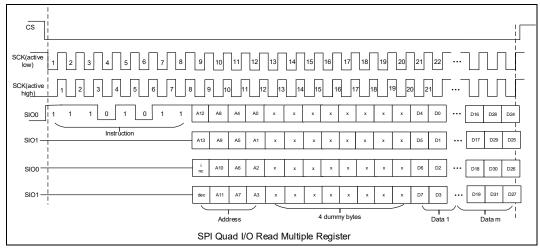

| Figure 7-14. SPI QUAD I/O READ                                  |      |

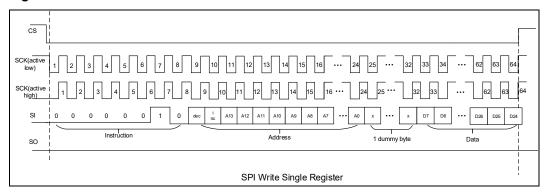

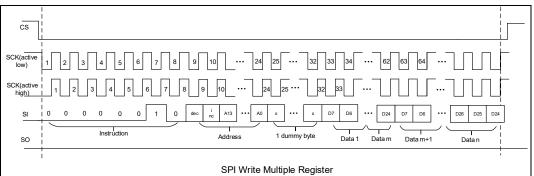

| Figure 7-15. SPI WRITE                                          |      |

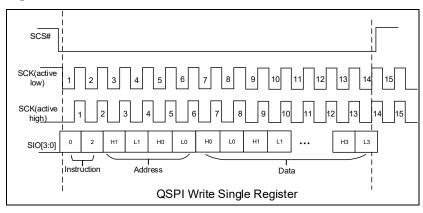

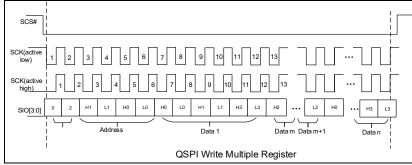

| Figure 7-16. QSPI WRITE                                         |      |

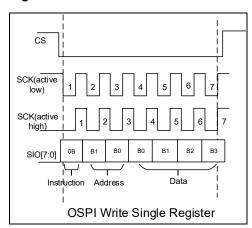

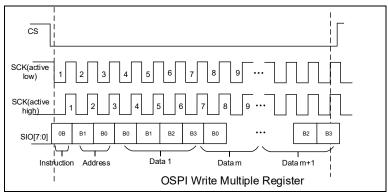

| Figure 7-17. OSPI WRITE                                         | . 93 |

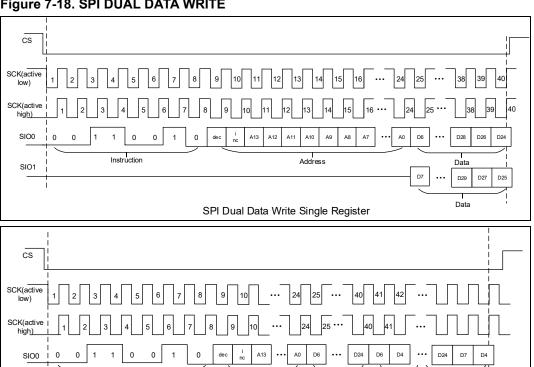

| Figure 7-18. SPI DUAL DATA WRITE                                |      |

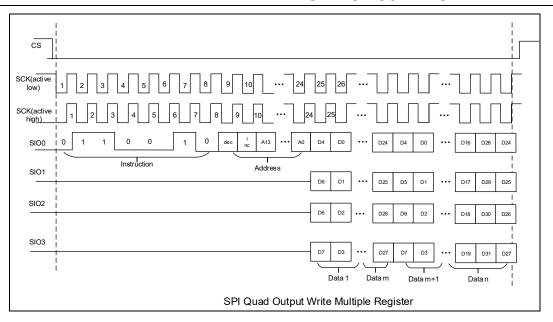

| Figure 7-19. SPI QUAD DATA WRITE                                |      |

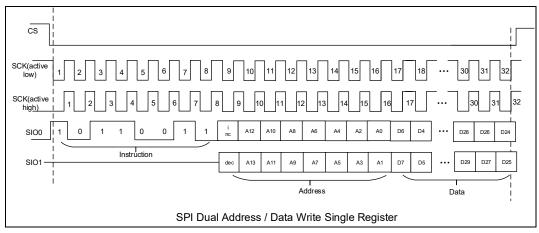

| Figure 7-20. SPI DUAL ADDRESS / DATA WRITE                      |      |

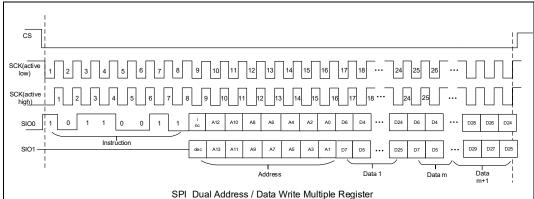

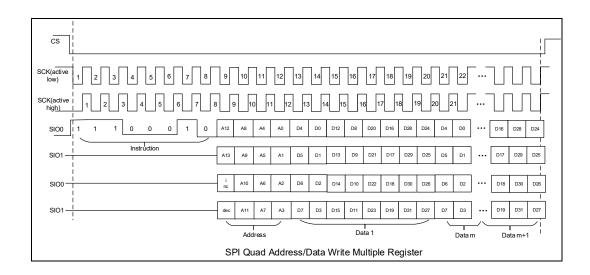

| Figure 7-21. SPI QUAD ADDRESS / DATA WRITE                      |      |

| Figure 7-22. The EXMC block diagram                             |      |

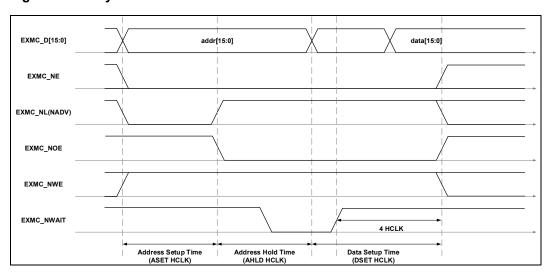

| Figure 7-23. Asynchronous write transmission                    |      |

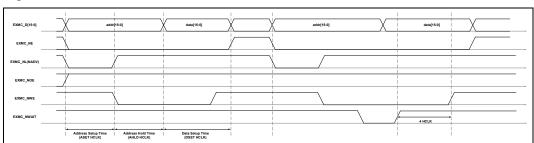

| Figure 7-24. Asynchronous read transmission                     | 102  |

| Figure 7-25. back-to-back transfers with nwait included         | 103  |

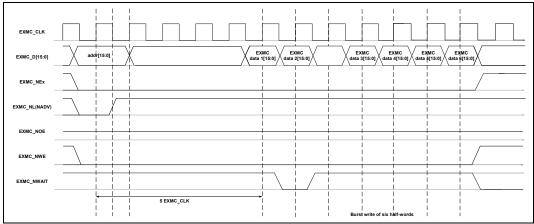

| Figure 7-26. Write transmission in sync mode                    |      |

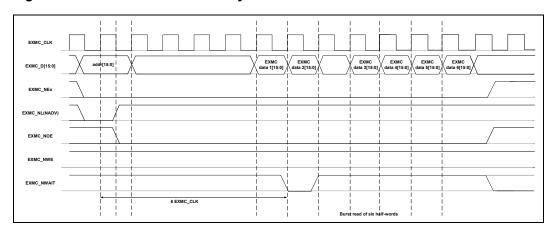

| Figure 7-27. Read transmission in sync mode                     | 104  |

| Figure 8-1.PHY functional block diagram                         | 106  |

| Figure 8-2. LED connect diagram                         | 108 |

|---------------------------------------------------------|-----|

| Figure 8-3. 100Base-TX LPI                              | 109 |

| Figure 9-1. EtherCAT system block diagram               | 156 |

| Figure 9-2. EtherCAT State Machine                      | 163 |

| Figure 9-3. EEPROM Layout                               | 164 |

| Figure 9-4. PDI Interrupt Masking and interrupt signals | 165 |

| Figure 9-5. EtherCAT Interrupt Masking                  | 166 |

# **List of Tables**

| Table 1-1. Memory map of GDSCN                                              | 13  |

|-----------------------------------------------------------------------------|-----|

| Table 1-2. Alignment of valid data                                          | 16  |

| Table 2-1. Power saving mode summary                                        | 33  |

| Table 5-1. GPIO configuration table                                         | 58  |

| Table 7-1. 4-wire mode                                                      | 77  |

| Table 7-2. 6-wire mode                                                      | 78  |

| Table 7-3. OSPI 8-line mode                                                 | 78  |

| Table 7-4. SPI instructions                                                 | 81  |

| Table 7-5. QSPI instruction                                                 | 81  |

| Table 7-6. OSPI instruction                                                 | 82  |

| Table 7-7. EXMC pin and description                                         | 101 |

| Table 9-1. PDIs for EtherCAT                                                | 158 |

| Table 9-2. Registers affected by PDI register function acknowledge by write | 159 |

| Table 10-1. Revision history                                                | 235 |

## 1. System and bus architecture

#### 1.1. Bus architecture

The bus architecture of ESC is shown in the following figure. The AHB matrix based on AMBA 5 AHB-LITE is a multi-layer AHB, which enables parallel access paths between one masters and multiple slaves in the system. One masters on the AHB decoder, including AHB bus of the PDI Wrapper. The AHB decoder consists of five slaves, including the AHB to OPB Bridge, EFUSE, AHB to APB Bridge, GPIO and RCU.

The AHB connects with the AHB peripherals including one AHB-to-APB bridges which provide full synchronous connections between the AHB decoder and the one APB buses. The one APB buses connect with all the APB peripherals, including the PMU, TIMER, SYSCFG, INTC.

PDI Wrapper FIFO Signal AHB Decoder:Fmax = 100MHz AHB to AHB to OPB **EFUSE GPIO** RCU **APB** Bridge Bridge PMU ESC\_CCTL EtherCAT IP APB:F<sub>max</sub> **TIMER** SYSCFG 100MHz INTC JDC

Figure 1-1. Bus architecture of ESC

## 1.2. Memory map

This section will introduce the memory distribution of GDSCN as shown in <u>Table 1-1</u>. Memory map of GDSCN below.

Table 1-1. Memory map of GDSCN

| Pre-defined | Address         | Peripherals                |

|-------------|-----------------|----------------------------|

| Regions     |                 | ·                          |

| EtherCAT    | 0x0000          | Туре                       |

|             | 0x0001          | Revision                   |

|             | 0x0002 - 0x0003 | Build                      |

|             | 0x0004          | FMMUs Supported            |

|             | 0x0005          | SyncManagers Supported     |

|             | 0x0006          | RAM Size                   |

|             | 0x0007          | Port Descriptor            |

|             | 0x0008 - 0x0009 | ESC Features Supported     |

|             | 0x0010 - 0x0011 | Configured Station Address |

|             | 0x0012 - 0x0013 | Configured Station Alias   |

|             | 0x0013 - 0x001F | Reserved                   |

|             | 0x0020          | Write Register Enable      |

|             | 0x0021          | Write Register Protection  |

|             | 0x0022 - 0x002F | Reserved                   |

|             | 0x0030          | ESC Write Enable           |

|             | 0x0031          | ESC Write Protection       |

|             | 0x0032 - 0x003F | Reserved                   |

|             | 0x0040          | ESC Reset ECAT             |

|             | 0x0041          | ESC Reset PDI              |

|             | 0x0042 - 0x0FF  | Reserved                   |

|             | 0x0100 - 0x0103 | ESC DL Control             |

|             | 0x0104 - 0x0107 | Reserved                   |

|             | 0x0108 - 0x0109 | Physical Read/Write Offset |

|             | 0x0110 - 0x0111 | ESC DL Status              |

|             | 0x0112 - 0x011F | Reserved                   |

|             | 0x0120 - 0x0121 | AL Control                 |

|             | 0x0122 - 0x012F | Reserved                   |

|             | 0x0130 - 0x0131 | AL Status                  |

|             | 0x0132 - 0x0133 | Reserved                   |

|             | 0x0134 - 0x0135 | AL Status Code             |

|             | 0x0136 - 0x0137 | Reserved                   |

|             | 0x0138          | RUN LED Override           |

|             | 0x0139          | Reserved                   |

|             | 0x0140          | PDI Control                |

|             | 0x0141          | ESC Configuration          |

|             | 0x0142 - 0x0143 | ASIC Configuration         |

|             | 0x0144 - 0x0145 | RESERVED Register          |

|             | 0x0146 - 0x014F | Reserved                   |

|             | 0x0150          | PDI Configuration          |

| Pre-defined | Address                            | Peripherals                                 |

|-------------|------------------------------------|---------------------------------------------|

| Regions     | Audress                            | i empirerais                                |

| Regions     | 0x0151                             | Sync/Latch PDI Configuration                |

|             | 0x0152 - 0x0153                    | Extended PDI Configuration                  |

|             | 0x0154 - 0x01FF                    | Reserved                                    |

|             | 0x0200 - 0x0201                    | ECAT Event Mask                             |

|             | 0x0202 - 0x0201                    | Reserved                                    |

|             | 0x0202 - 0x0203                    | PDI AL Event Mask                           |

|             | 0x0204 - 0x0207                    | Reserved                                    |

|             | 0x0230 - 0x0203                    | ECAT Event Request                          |

|             | 0x0210 - 0x0211                    | Reserved                                    |

|             | 0x0212 - 0x021F                    |                                             |

|             | 0x0220 - 0x0225<br>0x0223 - 0x022F | AL Event Request  Reserved                  |

|             | 0x0300 - 0x0307                    |                                             |

|             | 0x0300 - 0x0307<br>0x0308 - 0x030B | RX Error Counter Forwarded RX Error Counter |

|             |                                    |                                             |

|             | 0x030C                             | ECAT Processing Unit Error Counter          |

|             | 0x030D                             | PDI Error Counter  PDI Error Code           |

|             | 0x030E                             |                                             |

|             | 0x030F                             | Reserved                                    |

|             | 0x0310 - 0x0313                    | Lost Link Counter                           |

|             | 0x0314 - 0x03FF                    | Reserved                                    |

|             | 0x0400 - 0x0401                    | Watchdog Divider                            |

|             | 0x0410 - 0x0411                    | Watchdog Time PDI                           |

|             | 0x0420 - 0x0421                    | Watchdog Time Process Data                  |

|             | 0x0440 - 0x0441                    | Watchdog Status Process Data                |

|             | 0x0442                             | Watchdog Counter Process Data               |

|             | 0x0443                             | Watchdog Counter PDI                        |

|             | 0x0444 - 0x04FF                    | Reserved                                    |

|             | 0x0500                             | EEPROM Configuration                        |

|             | 0x0501                             | EEPROM PDI Access State                     |

|             | 0x0502 - 0x0503                    | EEPROM Control/Status                       |

|             | 0x0504 - 0x0507                    | EEPROM Address                              |

|             | 0x0508 - 0x050B                    | EEPROM Data                                 |

|             | 0x050C- 0x050F                     | Reserved                                    |

|             | 0x0510 - 0x0511                    | MII Management Control/Status               |

|             | 0x0512                             | PHY Address                                 |

|             | 0x0513                             | PHY Register Address                        |

|             | 0x0514 - 0x0515                    | PHY DATA                                    |

|             | 0x0516                             | MII Management ECAT Access State            |

|             | 0x0517                             | MII Management PDI Access State             |

|             | 0x0518 - 0x051B                    | PHY Port Status                             |

|             | 0x051C - 0x05FF                    | Reserved                                    |

| Pre-defined | Address         | Peripherals             |  |  |  |  |  |  |  |

|-------------|-----------------|-------------------------|--|--|--|--|--|--|--|

| Regions     |                 |                         |  |  |  |  |  |  |  |

|             | 0x0600 - 0x06FF | FMMU                    |  |  |  |  |  |  |  |

|             | 0x0700 - 0x07FF | Reserved                |  |  |  |  |  |  |  |

|             | 0x0800 - 0x087F | SyncManager             |  |  |  |  |  |  |  |

|             | 0x0880 - 0x08FF | Reserved                |  |  |  |  |  |  |  |

|             | 0x0900 - 0x09FF | Distributed Clocks (DC) |  |  |  |  |  |  |  |

|             | 0x0A00 - 0x0AFF | Reserved                |  |  |  |  |  |  |  |

|             | 0x0E00 - 0x0E07 | Product ID              |  |  |  |  |  |  |  |

|             | 0x0E08 - 0x0E0F | Vendor ID               |  |  |  |  |  |  |  |

|             | 0x0E10 - 0x0EFF | Reserved                |  |  |  |  |  |  |  |

|             | 0x0F00 - 0x0F03 | Digital I/O Output Data |  |  |  |  |  |  |  |

|             | 0x0F04 - 0x0F0F | Reserved                |  |  |  |  |  |  |  |

|             | 0x0F10 - 0x0F17 | General Purpose Outputs |  |  |  |  |  |  |  |

|             | 0x0F18 - 0x0F1F | General Purpose Inputs  |  |  |  |  |  |  |  |

|             | 0x0F20 - 0x0F7F | Reserved                |  |  |  |  |  |  |  |

|             | 0x0F80 - 0x0FFF | User RAM                |  |  |  |  |  |  |  |

|             | 0x1000 - 0x2FFF | Process Data RAM        |  |  |  |  |  |  |  |

| Peripheral  | 0x3300 - 0x33FF | AHB2OPB Bridge          |  |  |  |  |  |  |  |

|             | 0x3400 - 0x34FF | RCU                     |  |  |  |  |  |  |  |

|             | 0x3500 - 0x35FF | GPIO                    |  |  |  |  |  |  |  |

|             | 0x3600 - 0x36FF | EFUSE                   |  |  |  |  |  |  |  |

|             | 0x3700 - 0x37FF | PMU                     |  |  |  |  |  |  |  |

|             | 0x3800 - 0x38FF | TIMER                   |  |  |  |  |  |  |  |

|             | 0x3900 - 0x39FF | SYSCFG                  |  |  |  |  |  |  |  |

|             | 0x3A00 - 0x3AFF | INTC                    |  |  |  |  |  |  |  |

#### 1.3. AHB direct/indirect access

GDSCN can directly/indirectly access ESC registers and core PRAM through the AHB to OPB bridge in three ways: directly accessible ESC registers, indirectly accessible ESC core registers, and indirectly accessible ESC core PRAM. The bridge provides an AHB Slave interface towards the upstream side and OPB interfaces towards the downstream side of the ESC core, where the upstream AHB side is faster than, in frequency to, the downstream ESC core, and the clocks are synchronous in phase, and have an N:1(max N=16) frequency ratio.

#### 1.3.1. Direct AHB transmit access ESC register

Direct access to ESC registers is used for transferring data/commands to the indirect access of ESC core registers. When the AHB bus accesses the address range of 0x0000-0x0FFF, a single register read/write operation on the ESC core is initiated based on the CCTL\_RW bit in the ESC\_CCTL\_CMD register. At the start of a read cycle, the CCTL\_BUSY bit in the

ESC\_CCTL\_CMD register is set to 1, and at the end of the read cycle, CCTL\_BUSY is cleared to 0, allowing valid data to be read on the AHB bus. At the start of a write cycle, the CCTL\_BUSY bit is set to 1, valid data is written to the bus, and at the end of the write cycle, the CCTL BUSY bit is cleared, and the valid data is written into the register.

#### 1.3.2. Indirect transmit access ESC core register

GDSCN can access the ESC core registers indirectly through the ESC\_CCTL\_DATA and ESC\_CCTL\_CMD registers. When reading an ESC core register, the following steps are required: First, set the CCTL\_STOP bit in the ESC\_CCTL\_CMD register to 1 to clear the CCTL\_BUSY bit; set the CCTL\_RW bit in the ESC\_CCTL\_CMD register to 1, write the address of the register to be accessed into the CCTL\_ADDR field, and write the number of bytes to be read into the CCTL\_SIZE field, then set the CCTL\_BUSY bit to 1. When the CCTL\_BUSY bit is cleared, data can be read from the ESC\_CCTL\_DATA register.

When writing data to the ESC core registers, the following steps are required: First, set the CCTL\_STOP bit in the ESC\_CCTL\_CMD register to 1 to clear the CCTL\_BUSY bit; clear the CCTL\_RW bit in the ESC\_CCTL\_CMD register, write the address of the register to be accessed into the CCTL\_ADDR field, and write the number of bytes to be written into the CCTL\_SIZE field, then set the CCTL\_BUSY bit to 1. The configuration data can be written into the ESC\_CCTL\_CMD register at once. The completion of the write cycle is indicated by the CCTL\_BUSY bit being cleared to zero.

In the above read/write operations, the valid data is always aligned with the low bits of the ESC\_CCTL\_DATA. The valid data can be referred to the following table.

Table 1-2. Alignment of valid data

| CCTL_SIZE | ESC CCTL_ADDR[1:0] | ESC CCTL_DATA valid bytes        |

|-----------|--------------------|----------------------------------|

| 1         | 00/01/10/11        | [7:0]/ [15:8]/ [23:16]/ [31:24]/ |

| 2         | 00/10              | [15:0]/[31:16]                   |

| 4         | 00                 | [31:0]                           |

#### 1.3.3. Indirect transmit access ESC core PRAM

When initiating read operation to core PRAM through AHB, after writing PRAM start address and read length to ESC\_PRAM\_ALR register, PRAM\_BUSY\_READ is set to 1, the module starts to initiate multiple OPB read operations, read data from core PRAM and write to the TX FIFO. All OPB read operations are complete. PRAM\_BUSY\_READ is cleared. When data is transferred from the ESC core to the TX FIFO, the PRAM read length PRAM\_LEN\_READ and the PRAM read address PRAM\_ADDR\_READ are updated to show the process. Determines the valid bytes of the first read data according to the start address. Determines the valid bytes of the last read data based on the starting address and operation length. If necessary, the read command can be stopped by setting the ESC\_PRAM\_CR[PRAM\_STOP\_READ] bit to 1. If the OPB read period starts, the stop command takes effect after the current read operation is complete. After the stop

command takes effect, data in the TX FIFO is cleared.

When writing to the PRAM through AHB, after writing the RAM start address and write length to the ESC\_PRAM\_ALW register, write 1 to the PRAM\_BUSY\_WRITE bit of the ESC\_PRAM\_CW register, the module initiates multiple OPB write operations. Data is read from the RX FIFO and written to the core PRAM. All OPB write operations are complete. PRAM\_BUSY\_WRITE is cleared Write operations support wait mechanism, PRAM\_BUSY\_WRITE bit is set to 1, but when RX FIFO is empty, OPB module will not immediately initiate OPB transfer operation, until there is data in RX FIFO will initiate this operation. After each OPB ACK response, it will detect the RX FIFO state. If the RX FIFO is empty, it will enter the waiting state and enter the next transmission operation until there is data. When data is transferred from the RX FIFO to the core, the PRAM write length PRAM\_LEN\_WRITE and the PRAM write address PRAM\_ADDR\_WRITE are updated to show the process. Determines the valid bytes of the first data write according to the start address. Based on the starting address and operation length, determines the valid bytes of the last data write.

If necessary, the write command can be stopped by setting the PRAM\_STOP\_WRITE bit to 1. If the OPB write cycle starts, the stop command takes effect after the read operation is complete. After the stop command takes effect, data in the RX FIFO is cleared.

### 1.4. Register protection in BUSY state

If the BUSY related register bits, such as CCTL\_BUSY, PRAM\_BUSY\_READ, and PRAM\_BUSY\_WRITE, are set to 1, you can set the BRP bit to protect the register from rewriting. When CCTL\_BUSY is set to 1, ESC\_CCTL\_DATA/ ESC\_CCTL\_CMD is protected from rewriting by AHB write operations. When PRAM\_BUSY\_READ is set to 1, ESC\_PRAM\_ALR is protected from rewriting by AHB write operations. When PRAM\_BUSY\_WRITE is set to 1, ESC\_PRAM\_ALW is protected from being overwritten by AHB write operations

When the BRP bit is set to 1, when the BUSY related register bit is set to 1, the user's AHB write operation to the corresponding register will be lost, then the WDLF flag in the ESC\_OPB\_CS register is set to 1, and the interrupt will be triggered when the WDIE bit is set to 1.

When the BRP bit is set to 0, when the BUSY related register bit is set to 1, the user's AHB write operation to the corresponding register will cause the current OPB transmission error, then the WEF flag in the ESC\_OPB\_CS register is set to 1, and the interrupt will be triggered when the WEIE bit is set to 1. It is advised to handle it as soon as possible to avoid more errors.

#### 1.5. OPB transmission timeout function

The OPB transmission timeout function can be enabled by setting the TOEN bit in the ESC\_OPB\_CS register to 1. The timeout interval can be configured by the TO\_CNT bit in the ESC\_OPB\_CS register. When the counter exceeds the TO\_CNT programming value, the TOF flag in the ESC\_OPB\_CS register is set to 1. If the TOIE bit in the ESC\_OPB\_CS register is set to 1, a timeout interrupt is generated. Timeout interrupt response processing:

- 1. If the ESC CCTL direct read/write mode is used, the TOF flag is set after a timeout interrupt response occurs. Terminate the transmission directly to avoid the BUS being occupied.

- 2. If the ESC CCTL is used in indirect read/write mode, the TOF flag is set after a timeout interrupt response occurs. You can stop this operation by writing 1 to the ESC CCTL STOP bit.

- 3. When the PRAM is used in indirect read/write mode, the TOF flag is set after a timeout interrupt response occurs. You can stop this operation by writing 1 to the PRAM\_STOP\_WRITE/ PRAM\_STOP\_READ bit.

#### 1.6. EFUSE function

The EFUSE controller has EFUSE macro that store system paramters. As a non-volatile unit of storage, the bit of EFUSE macro cannot be restored to 0 once it is programmed to 1. According to the software opration, the EFUSE controller can program all bits in the system parameters.

The main purposes of the EFUSE are the following:

- One-time programmable nonvolatile EFUSE storage cells organized as 32\*8bit

- All bits in the EFUSE cannot be rollback from 1 to 0.

- Can only be accessed through corresponding register.

Figure 1-2 Efuse controller block diagram

## 1.7. EFUSE Register definition

EFUSE base address: 0x3600

## 1.7.1. Chip id register (EF\_CHIP\_ID)

Address offset: 0x14 Reset value: 0x0000 0000

This register has to be accessed by word (32-bit)

| 31 | 30               | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|    | Reserved         |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|    | r                |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 15 | 14               | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|    | EF_CHIP_ID[15:0] |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

Bits Fields Descriptions

31:16 Reserved Must be kept at reset value.

15:0 EF\_CHIP\_ID[15:0] Read CHIP ID

## 1.7.2. EFUSE UID READ register (EFUSE\_UID\_READ)

Address offset: 0x1C+X\*4(X=0,1,2,3)

Reset value: 0x0000 0000

This register has to be accessed by word (32-bit)

| 31 | 30               | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|    | EF_UID_RD[31:16] |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|    | r                |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 15 | 14               | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|    | EF_UID_RD[15:0]  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

r

| Bits | Fields          | Descriptions     |

|------|-----------------|------------------|

| 31:0 | EF UID RD[31:0] | Read the ESC UID |

## 1.8. ESC core controller (ESC\_CCTL)

The main purposes of the ESC core controller (ESC CCTL) are the following:

- Configuring indirect transmit access of the ESC core register

- Configuring indirect transmit access of the ESC core PRAM.

## 1.9. ESC core controller register definition

ESC core control register base address: 0x3300

#### 1.9.1. ESC CCTL data register (ESC\_CCTL\_DATA)

Address offset: 0x00

Reset value: 0x0000 0000

This register has to be accessed by word (32-bit).

| 31 | 30               | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|    | CCTL_DATA[31:16] |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| rw |                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 15 | 14               | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|    | CCTL_DATA[15:0]  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

rw

| Bits | Fields          | Descriptions                                                                   |

|------|-----------------|--------------------------------------------------------------------------------|

| 31:0 | CCTL_DATA[31:0] | ESC CCTL data                                                                  |

|      |                 | This field indicate the value read from or written to the ESC Core. Reading or |

This field indicate the value read from or written to the ESC Core. Reading or writing depends on the ESC\_CCTL\_CMD[CCTL\_RW] bit. If the CCTL\_RW bit is 1, this value is the data read from the ESC Core; If the CCTL\_RW bit is 0, this value

is the data written to the ESC Core.

The low bit of this filed always indicates the valid data written or read.

## 1.9.2. ESC CCTL command register (ESC\_CCTL\_CMD)

Address offset: 0x04

Reset value: 0x0000 0000

This register has to be accessed by word (32-bit).

| 31     | 30      | 29      | 28 | 27                      | 26 | 25 | 24      | 23        | 22 | 21 | 20 | 19 | 18 | 17 | 16 |  |

|--------|---------|---------|----|-------------------------|----|----|---------|-----------|----|----|----|----|----|----|----|--|

| CCTL_B |         | CCTL_ST |    | Pesenied CCTI SIZEI2:01 |    |    |         |           |    |    |    |    |    |    |    |  |

| USY    | CCTL_RW | OP      |    | Reserved CCTL_SIZE[2:0] |    |    |         |           |    |    |    |    |    |    |    |  |

| rw     | rw      | rw      |    |                         |    |    |         |           |    |    |    |    |    |    |    |  |

| 15     | 14      | 13      | 12 | 11                      | 10 | 9  | 8       | 7         | 6  | 5  | 4  | 3  | 2  | 1  | 0  |  |

|        |         |         |    |                         |    |    | CCTL AI | DDR[15:0] |    |    |    |    |    |    |    |  |

|        |         |         |    |                         |    |    | _       |           |    |    |    |    |    |    |    |  |

rw

| Bits  | Fields          | Descriptions                                                                             |

|-------|-----------------|------------------------------------------------------------------------------------------|

| 31    | CCTL_BUSY       | CCTL Busy. There is no effect if the bit is written to zero                              |

|       |                 | 0: No read/write (according to CCTL_RW) operation is being performed.                    |

|       |                 | 1: Read/write operation is being performed.                                              |

|       |                 | Note: When the read/write operation is complete, this bit will be cleared. Then the      |

|       |                 | valid data is available for the HOST to read from ESC_CCTL_DATA or write to              |

|       |                 | ESC_CCTL_DATA register. It is required that ESC_CCTL_CMD and                             |

|       |                 | ESC_CCTL_DATA registers are modified R when this bit is 0.                               |

| 30    |                 | Read operation or write operation                                                        |

|       | CCTL_RW         | 0: Write operation                                                                       |

|       |                 | 1: Read operation                                                                        |

| 29    | CCTL_STOP       | Stop read operation or write operation. There is no effect if the bit is written to zero |

|       |                 | 0: No effect                                                                             |

|       |                 | 1: Stop the ESC core register reading or writing operation                               |

|       |                 | Note: When the CCTL_BUSY is cleared, the CCTL_STOP will be cleared                       |

| 28:19 | Reserved        | Must be kept at reset value.                                                             |

| 18:16 | CCTL_SIZE[2:0]  | This field specifies the ESC CCTL size (byte)。 1, 2 and 4 are valid, other values        |

|       |                 | are invalid. More details refer to <u>Table 1-2. Alignment of valid data</u>             |

| 15:0  | CCTL_ADDR[15:0] | This field specifies the addresses of ESC core registers that will be accessed           |

## 1.9.3. ESC PRAM FIFO data read register (ESC\_PRAM\_FIFO\_DR)

Address offset: 0x10

Reset value: 0x0000 0000

|    |                           | This re | egister | has to | be acc | essed | by wor   | d (32-b  | it).   |    |    |    |    |    |    |

|----|---------------------------|---------|---------|--------|--------|-------|----------|----------|--------|----|----|----|----|----|----|

| 31 | 30                        | 29      | 28      | 27     | 26     | 25    | 24       | 23       | 22     | 21 | 20 | 19 | 18 | 17 | 16 |

|    |                           |         |         |        |        | PRAM  | /_FIFO_D | TA_READ[ | 31:16] |    |    |    |    |    |    |

|    | rw                        |         |         |        |        |       |          |          |        |    |    |    |    |    |    |

| 15 | 14                        | 13      | 12      | 11     | 10     | 9     | 8        | 7        | 6      | 5  | 4  | 3  | 2  | 1  | 0  |

|    | PRAM_FIFO_DATA_READ[15:0] |         |         |        |        |       |          |          |        |    |    |    |    |    |    |

rw

| Bits | Fields          | Descriptions                                                                 |

|------|-----------------|------------------------------------------------------------------------------|

| 31:0 | PRAM_FIFO_DATA_ | Data read from ESC PRAM.                                                     |

|      | READ[31:0]      | The valid value of data is determined according to the start address and the |

|      |                 | transfer length.                                                             |

## 1.9.4. ESC PRAM address and length read register (ESC\_PRAM\_ALR)

Address offset: 0x14

Reset value: 0x0000 0000

This register has to be accessed by word (32-bit).

| 31 | 30                    | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|-----------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|    | PRAM_LEN_READ[15: 0]  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|    | rw                    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 15 | 14                    | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|    | PRAM_ADDR_READ [15:0] |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

rw

| Bits  | Fields       | Descriptions                                                                      |

|-------|--------------|-----------------------------------------------------------------------------------|

| 31:16 | PRAM_LEN_REA | D[1 Data length read from ESC PRAM in bytes. This field is decremented as data is |

|       | 5: 0]        | read into the FIFO.                                                               |

|       |              | <b>Note:</b> When PRAM_BUSY_READ is 1, this field cannot be modified.             |

| 15:0  | PRAM_ADDR_RE | AD ESC PRAM data read address. This field is incremented as data is read into the |

|       | [15:0]       | FIFO.                                                                             |

|       |              | Note: When PRAM BUSY READ is 1, this field cannot be modified.                    |

## 1.9.5. ESC PRAM command read register (ESC\_PRAM\_CR)

Address offset: 0x18 Reset value: 0x0000 0000

This register has to be accessed by word (32-bit).

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

| PRAM_B | PRAM_ST | Reserved |

|--------|---------|----------|

| USY_RE | OP_READ |          |

| Bits  | Fields         | Descriptions                                                                     |

|-------|----------------|----------------------------------------------------------------------------------|

| 31    | PRAM_BUSY_READ | Whether the PRAM is being read. There is no effect if the bit is written to zero |

|       |                | 0: No PRAM read operation                                                        |

|       |                | 1: PRAM is being read                                                            |

|       |                | <b>Note:</b> This bit is cleared when the read operation is complete.            |

| 30    | PRAM_STOP_READ | Stop PRAM read operation. There is no effect if the bit is written to zero       |

|       |                | 0: No effect                                                                     |

|       |                | 1: Stop the PRAM reading operation                                               |

|       |                | Note: After this bit is set to 1, the PRAM_BUSY_READ is cleared, and the RX      |

|       |                | FIFO is reset. Then this bit will self-clear.                                    |

| 29:13 | Reserved       | Must be kept at reset value.                                                     |

| 12:8  | PRAM_DATA_CNT_ | PRAM data read valid count                                                       |

|       | READ[4:0]      | This count increases as data is read from the PRAM to the RX FIFO and            |

|       |                | decreases as data of the entire DWORD size is read from the RX FIFO              |

| 7:1   | Reserved       | Must be kept at reset value.                                                     |

| 0     |                | A PRAM valid data read                                                           |

|       | _READ          | 0: There is no valid data to be read.                                            |

|       |                | 1: There is valid data to be read.                                               |

## 1.9.6. ESC PRAM FIFO data write register (ESC\_PRAM\_FIFO\_DW)

Address offset: 0x20 Reset value: 0x0000 0000

This register has to be accessed by word (32-bit).

| 31 | 30 | 29 | 28 | 27 | 26 | 25   | 24        | 23        | 22      | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----|----|----|----|----|------|-----------|-----------|---------|----|----|----|----|----|----|

|    |    |    |    |    |    | PRAM | 1_FIFO_DA | TA_WRITE  | [31:16] |    |    |    |    |    |    |

|    |    |    |    |    |    |      | r         | w         |         |    |    |    |    |    |    |

| 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8         | 7         | 6       | 5  | 4  | 3  | 2  | 1  | 0  |

|    |    |    |    |    |    | PRAM | M_FIFO_D/ | ATA_WRITE | [15:0]  |    |    |    |    |    |    |

rw

| Bits | Fields          | Descriptions            |

|------|-----------------|-------------------------|

| 31:0 | PRAM_FIFO_DATA_ | Data write to ESC PRAM. |

WRITE[31:0]

The valid value of data is determined according to the start address and the transfer length.

## 1.9.7. ESC PRAM address and length write register (ESC\_PRAM\_ALW)

Address offset: 0x24 Reset value: 0x0000 0000

This register has to be accessed by word (32-bit).

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24       | 23         | 22   | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----|----|----|----|----|----|----------|------------|------|----|----|----|----|----|----|

|    |    |    |    |    |    | P  | RAM_LEN_ | WRITE[15:  | 0]   |    |    |    |    |    |    |

|    |    |    |    |    |    |    | r        | w          |      |    |    |    |    |    |    |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8        | 7          | 6    | 5  | 4  | 3  | 2  | 1  | 0  |

|    |    |    |    |    |    | PF | AM_ADDR  | L_WRITE[15 | 5:0] |    |    |    |    |    |    |

rw

| Bits  | Fields         | Descriptions                                                                    |

|-------|----------------|---------------------------------------------------------------------------------|

| 31:16 | PRAM_LEN_WRITE | Data length written to ESC PRAM in bytes. This field is decremented as data is  |

|       | 15: 0]         | written into the FIFO.                                                          |

|       |                | <b>Note:</b> When PRAM_BUSY_WRITE is 1, this field cannot be modified.          |

| 15:0  | PRAM_ADDR_WRIT | ESC PRAM data write address. This field is incremented as data is read from the |

|       | E[15:0]        | FIFO.                                                                           |

Note: When PRAM\_BUSY\_WRITE is 1, this field cannot be modified.

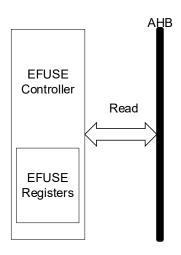

#### 1.9.8. ESC PRAM command write register (ESC\_PRAM\_CW)

Address offset: 0x28

Reset value: 0x0000 1001

This register has to be accessed by word (32-bit).

| 31     | 30       | 29 | 28 | 27      | 26        | 25         | 24 | 23   | 22    | 21 | 20       | 19 | 18 | 17 | 16       |

|--------|----------|----|----|---------|-----------|------------|----|------|-------|----|----------|----|----|----|----------|

| PRAM_B | PRAM_ST  |    |    |         |           |            |    |      |       |    |          |    |    |    |          |

| USY_WR | OP_WRIT  |    |    |         |           |            |    | Rese | erved |    |          |    |    |    |          |

| ITE    | Е        |    |    |         |           |            |    |      |       |    |          |    |    |    |          |

| rw     | rw       |    |    |         |           |            |    |      |       |    |          |    |    |    |          |

| 15     | 14       | 13 | 12 | 11      | 10        | 9          | 8  | 7    | 6     | 5  | 4        | 3  | 2  | 1  | 0        |

|        |          |    |    |         |           |            |    |      |       |    |          |    |    |    | PRAM_VA  |

|        | Reserved |    |    | PRAM_VA | LID_CNT_V | VRITE[4:0] |    |      |       |    | Reserved |    |    |    | LID_WRIT |

|        |          |    |    |         |           |            |    |      |       |    |          |    |    |    | E        |

Bits Fields Descriptions

PRAM\_BUSY\_WRIT Whether the PRAM is being written. There is no effect if the bit is written to zero

E 0: No PRAM write operation

|       |                 | OBCONOCEAN COOL Manage                                                         |

|-------|-----------------|--------------------------------------------------------------------------------|

| _     |                 | 1: PRAM is being writing                                                       |

|       |                 | <b>Note:</b> This bit is cleared when the write operation is complete.         |

| 30    | PRAM_STOP_WRIT  | Stop PRAM write operation. There is no effect if the bit is written to zero    |

|       | E               | 0: No effect                                                                   |

|       |                 | 1: Stop the PRAM writing operation                                             |

|       |                 | Note: After this bit is set to 1, the PRAM_BUSY_WRITE is cleared, and the TX   |

|       |                 | FIFO is reset. Then this bit will self-clear.                                  |

| 29:13 | Reserved        | Must be kept at reset value.                                                   |

| 12:8  | PRAM_VALID_CNT_ | PRAM data write valid count                                                    |

|       | WRITE[4:0]      | This count increases as data is read from the TX FIFO to PRAM and decreases as |

|       |                 | data of the entire DWORD size is written to the PRAM                           |

| 7:1   | Reserved        | Must be kept at reset value.                                                   |

| 0     | PRAM_VALID_DATA | PRAM valid data write                                                          |

|       | _WRITE          | 0: There is no valid data to be written                                        |

|       |                 |                                                                                |

1: There is valid data to be written.

## 1.9.9. ESC OPB control and status register (ESC\_OPB\_CS)

Address offset: 0x30 Reset value: 0x0000 0479

This register has to be accessed by word (32-bit).

| 31   | 30       | 29   | 28    | 27  | 26   | 25  | 24          | 23      | 22       | 21          | 20 | 19   | 18    | 17 | 16          |

|------|----------|------|-------|-----|------|-----|-------------|---------|----------|-------------|----|------|-------|----|-------------|

| RAAF | RAAIE    | WDLF | WDLIE | TOF | TOIE | WEF | WEIE        | ESC     | ESC      |             |    |      |       |    |             |

|      |          |      |       |     |      |     |             | CCTLIVF | CCTLIVIE |             |    | Rese | erved |    |             |

| rw   | rw       | rw   | rw    | rw  | rw   | rw  | rw          | rw      | rw       |             |    |      |       |    |             |

| 15   | 14       | 13   | 12    | 11  | 10   | 9   | 8           | 7       | 6        | 5           | 4  | 3    | 2     | 1  | 0           |

|      | Reserved |      |       |     |      |     | TO_CNT[8:0] |         |          |             |    |      |       |    |             |

|      |          |      |       |     | nu.  |     |             |         |          | <b>5</b> 14 |    |      |       |    | <b>5</b> 14 |

| Bits | Fields | Descriptions                                                                      |

|------|--------|-----------------------------------------------------------------------------------|

| 31   | RAAF   | Reserved address access flag. This flag will be triggered when the access address |

|      |        | is a reserved address segment. This flag can be cleared by writing 1.             |

|      |        | 0: The access address is a valid address segment                                  |

|      |        | 1: The access address is a reserved address segment                               |

| 30   | RAAIE  | Reserved address access interrupt enable                                          |

|      |        | 0: Interrupt is inhibited                                                         |

|      |        | 1: An interrupt will occur whenever the RAAF bit is set                           |

| 29   | WDLF   | Write data lost flag. when BRP enable, AHB write operation will cause data lose   |

| digabevice | <b>-</b>     | GD3CN032XX User Mariuar                                                                        |

|------------|--------------|------------------------------------------------------------------------------------------------|

|            |              | when the busy bit is high, this flag will be triggered. This flag can be cleared by writing 1. |

|            |              | 0: No data lost                                                                                |

|            |              | 1: The data in this transmission is lost                                                       |

| 28         | WDLIE        | Write data lost interrupt enable                                                               |

|            |              | 0: Interrupt is inhibited                                                                      |

|            |              | 1: An interrupt will occur whenever the RAAF bit is set                                        |

| 27         | TOF          | Time out flag, when single transmission time exceeds the programmed value, this                |

|            |              | flag will be triggered. This flag can be cleared by writing 1.                                 |

|            |              | 0: No ESC core timeout transmission occurred                                                   |

|            |              | 1: An ESC core timeout transmission occurred                                                   |

| 26         | TOIE         | Timer out interrupt enable                                                                     |

|            |              | 0: Interrupt is inhibited                                                                      |

|            |              | 1: An interrupt will occur whenever the RAAF bit is set                                        |

| 25         | WEF          | write error flag. when BRP disable, AHB write operation will cause current OPB                 |

|            |              | transmission error when the busy bit is high, this flag will be triggered. This flag can       |

|            |              | be cleared by writing 1.                                                                       |

| 24         | WEIE         | Write error interrupt enable.                                                                  |

|            |              | 0: Interrupt is inhibited                                                                      |

|            |              | 1: An interrupt will occur whenever the WEF bit is set                                         |

| 23         | ESC CCTLIVF  | CCTL_SIZE & CCTL_ADDR illegal value flag. The CCTL_SIZE and CCTL_ADDR                          |

|            |              | value written to the register does not meet the requirement, causing this transfer to          |

|            |              | not occur, this flag will be triggered. This flag can be cleared by writing 1.                 |

| 22         | ESC CCTLIVIE | CCTL_SIZE & CCTL_ADDR Illegal value interrupt enable.                                          |

|            |              | 0: Interrupt is inhibited                                                                      |

|            |              | 1: An interrupt will occur whenever the IESC CCTLVF bit is set                                 |

| 21:11      | Reserved     | Must be kept at reset value.                                                                   |

| 10         | BRP          | When busy bit is high, prevent register change                                                 |

|            |              | 1: the protection takes effect                                                                 |

|            |              | 0: the protection does not take effect                                                         |

| 9:1        | TO_CNT[8:0]  | Time Out counter                                                                               |

|            |              | This field indicates the transmission timeout in bits during which no ACK response             |

|            |              | was received; The programmer data cannot be less than the minimum value                        |

|            |              | recommended the manual(60).                                                                    |

| 0          | TOEN         | Time Out enable                                                                                |

|            |              | This field indicates that whether the function is effect                                       |

|            |              | 1: Timeout feature enabled                                                                     |

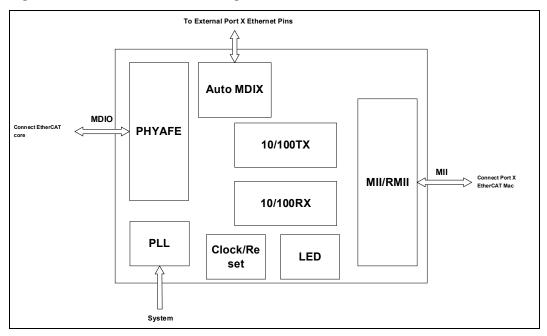

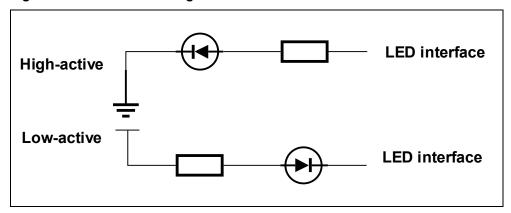

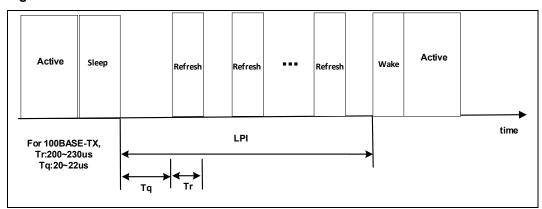

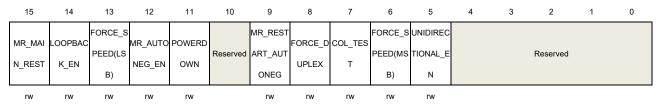

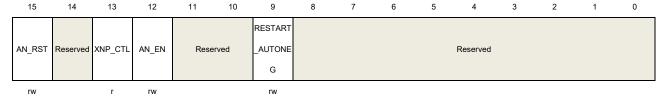

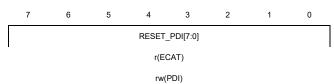

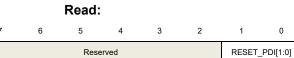

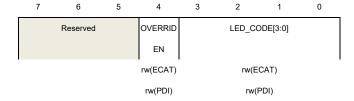

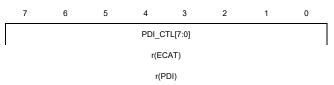

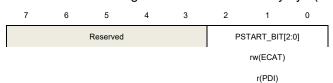

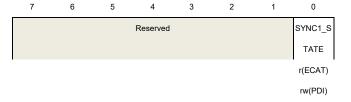

0: Timeout feature disabled.