# GigaDevice Semiconductor Inc.

# GD30SP2200x OVP Load Switch with Adjustable OVLO

**Datasheet**

## **Table of Contents**

| I      | able ( | of Contents                          | 2  |

|--------|--------|--------------------------------------|----|

| L      | ist of | f Figures                            | 4  |

|        |        | f Tables                             |    |

| _<br>1 |        | atures                               |    |

|        |        |                                      |    |

| 2      | _      | pplications                          |    |

| 3      | Ge     | eneral description                   | 6  |

| 4      | De     | evice overview                       | 7  |

|        | 4.1    | Device information                   | 7  |

|        | 4.2    | Block diagram                        | 7  |

|        | 4.3    | Pinout and pin assignment            |    |

|        | 4.4    | Pin definitions                      |    |

| 5      | Fu     | Inctional description                | 9  |

|        | 5.1    | Detailed Description                 |    |

|        | 5.1    |                                      |    |

|        | 5.1    |                                      |    |

|        | 5.1    |                                      |    |

|        | 5.2    | Application information              | 10 |

|        | 5.2    | • •                                  |    |

|        | 5.2    | .2 Input capacitor selection         | 10 |

|        | 5.2    | .3 Output capacitor selection        | 10 |

| 6      | Ele    | ectrical characteristics             | 11 |

|        | 6.1    | Absolute maximum ratings             | 11 |

|        | 6.2    | Recommended operation conditions     | 11 |

|        | 6.3    | Electrical sensitivity               | 11 |

|        | 6.4    | Power supplies voltages and currents |    |

|        | 6.5    | Protections                          |    |

|        | 6.6    | Timing Diagram                       |    |

|        | 6.7    | Typical Characteristics              |    |

| 7      |        | pical application circuit            |    |

|        |        | • • • •                              |    |

| 8      | ,      | yout guideline                       |    |

| 9      | Pa     | ckage information                    | 19 |

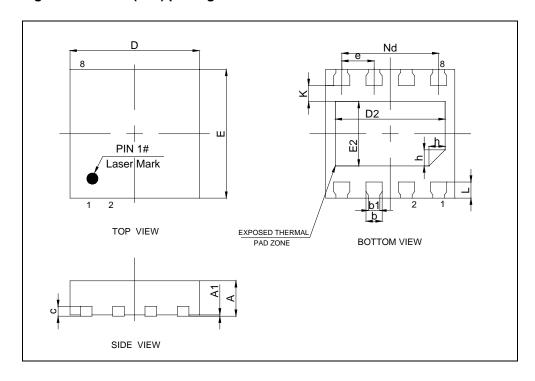

| 9.1 | DFN8L(2X2) package outline dimensions | 19 |

|-----|---------------------------------------|----|

|     | Thermal characteristics               |    |

|     | Ordering information                  |    |

|     | Revision history                      |    |

|     |                                       |    |

# **List of Figures**

| Figure 4-1 Block diagram for GD30SP2200x           | 7  |

|----------------------------------------------------|----|

| Figure 4-2 GD30SP2200x DFN8L(2X2) pinouts          |    |

| Figure 5-1 Feedback resistor divider               | 10 |

| Figure 6-1 Timing Diagram                          |    |

| Figure 7-1 Typical GD30SP2200x Application Circuit | 17 |

| Figure 9-1 DFN8L(2X2) package outline              | 19 |

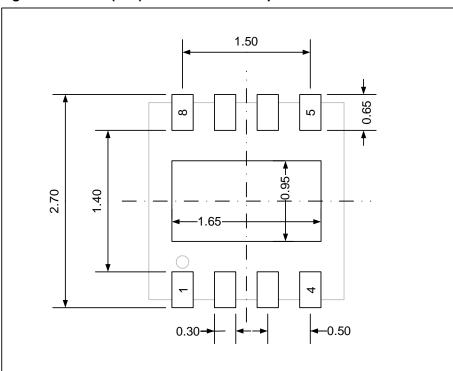

| Figure 9-2 DFN8L(2X2) recommended footprint        | 20 |

## **List of Tables**

| Table 4-1 Device Information for GD30SP2200x                   | 7  |

|----------------------------------------------------------------|----|

| Table 4-2. GD30SP2200x DFN8L(2X2) pin definitions              | 8  |

| Table 6-1 Absolute maximum ratings                             | 11 |

| Table 6-2 Recommended operation conditions                     | 11 |

| Table 6-3 Electrostatic Discharge and Latch-up characteristics | 11 |

| Table 6-4 Power supplies voltages and currents                 | 12 |

| Table 6-5 Over temperature characteristics                     | 12 |

| Table 9-1 DFN8L(2X2) package dimensions (in mm)                | 19 |

| Table 9-2 Package Thermal Characteristics(1)                   | 21 |

| Table 10-1 Part order code for GD30SP2200x devices             | 22 |

| Table 11-1 Revision history                                    | 23 |

#### 1 Features

- 2.5V to 30V Wide Input Voltage Range

- Up to 3A output current

- 100µA Low Quiescent Current

- Internal Fixed OVLO threshold 6.8V

- Wide Adjustable OVLO Threshold Range from 4V to 15V

- Low  $R_{DS\_ON}$  for Internal Switches :50m $\Omega$

- Fast Turn-off Response time when OVP: 450ns

- Over Temperature Protection

- RoHS Compliant and Halogen Free

- Compact Package: DFN8L(2X2)

## 2 Applications

- True Wireless Stereo (TWS)

- Bluetooth Speaker

- Portable and mobile devices

- Smart phones

- Low voltage peripherals

## 3 General description

The GD30SP2200x is an Over-Voltage-Protection (OVP) load switch of  $50m\Omega$  with adjustable over-voltage-lock-out (OVLO) threshold voltage. The device will turn off the internal MOSFET switch in a fast response of 450ns when the input voltage is over the pre-set OVLO threshold.

When the OVLO is connected to GND, the internal fixed OVLO threshold is set at 6.8V. The OVLO threshold voltage can be adjusted with an external resistor divider and the range is between 4V and 15V. The IC allows a maximum 3A current from IN to OUT. An over temperature protection (OTP) function is implemented internally and monitors the chip temperature to protect the device.

The GD30SP2200x is available in a green small foot print DFN8L(2X2) package.

## 4 Device overview

#### 4.1 Device information

Table 4-1 Device Information for GD30SP2200x

| Part Number | Package    | Function                | Description                     |

|-------------|------------|-------------------------|---------------------------------|

| GD30SP2200x | DFN8L(2X2) | Over Voltage Protection | OVP Load Switch with Adjustable |

| GD303P2200X | DFNoL(2X2) | Over-Voltage-Protection | OVLO                            |

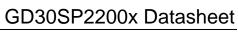

## 4.2 Block diagram

Figure 4-1 Block diagram for GD30SP2200x

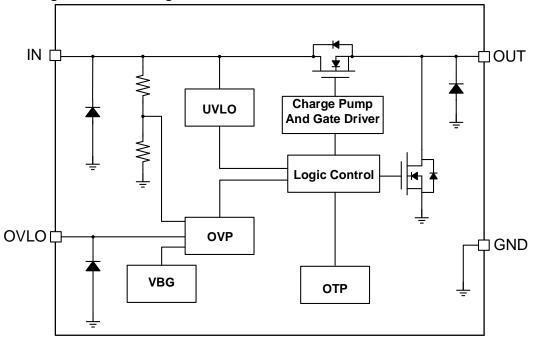

## 4.3 Pinout and pin assignment

Figure 4-2 GD30SP2200x DFN8L(2X2) pinouts

#### 4.4 Pin definitions

Table 4-2. GD30SP2200x DFN8L(2X2) pin definitions

| Pin Name | Pins  | Pin Type | Functions description                                                                                                                        |

|----------|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| OUT      | 1,2,3 | 0        | Output of the Regulator. A general 1uF ceramic capacitor should be placed as close as possible to this pin.                                  |

| GND      | 4     | G        | <b>Ground</b> . The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                          |

| OVLO     | 5     | I/O      | <b>OVLO Threshold Set</b> . Connect a resistor-divider to set different OVLO threshold, VovLo=1.2x(1+R1/R2) as shown in typical application. |

| IN       | 6,7,8 | I        | <b>Power Supply Voltage Input</b> . A general 1uF ceramic capacitor should be placed as close as possible to this pin.                       |

| PowerPAD | 9     | G        | Thermal pad. connect to ground.                                                                                                              |

#### Notes:

(1) Type: I = input, O = output, I/O = input or output, G = Ground.

## 5 Functional description

#### 5.1 Detailed Description

The GD30SP2200x is placed between the power supply and the low-voltage load to be protected. The device consists of a slew-rate controlled, low resistance OVP switch of typical  $50m\Omega$  and over-voltage monitor and protection (OVLO). The device can protect low voltage systems against voltage faults up to 28V. If the input voltage exceeds the OVLO threshold, the internal switch is turned off to prevent damage to downstream components. A 16ms debounce time is built into the device to prevent false turn-on of the internal switch during startup.

In normal operation the OVP switch acts as a slew-rate controlled load switch, connecting and disconnecting the power supply from IN to OUT. A low resistance N-channel MOSFET is utilized to minimize the voltage drop between the voltage source and the load and to reduce power dissipation. When the input voltage is over the programmed OVLO threshold, the device turns off the internal switch in a fast response of 450ns and disconnects the load from the abnormal input, preventing damage to downstream components.

Other protection features implemented in the device include over temperature protection. In the event that the power dissipation causes the IC temperature to exceed its maximum temperature setting, the GD30SP2200x will turn off.

#### 5.1.1 Internal Switch

The GD30SP2200x incorporate an internal N-MOSFET with a  $50m\Omega$  (TYP) R<sub>on</sub>. The MOSFET is driven by an integrated charge pump which generates the necessary voltage above IN.

#### 5.1.2 OVLO threshold

The GD30SP2200x has a 1.2V over-voltage trip reference on the OVLO pin. With a resistor-divider on OVLO pin from IN to GND, the over-voltage protection point of IN can be programmed between 4V and 15V. Fixed OVLO threshold is set with an internal resistor-divider providing a 6.8V-threshold. To activate the internal fixed OVP, the OVLO pin should be connected to GND.

#### 5.1.3 Protection features

To avoid mis-operation of the device at low input voltages, the GD30SP2200x shuts down at voltages lower than Vuvlo with Vuvlo\_HYS hysteresis.

The GD30SP2200x enters thermal shutdown once the junction temperature exceeds typically  $T_{OT}$ . Once the device temperature falls below the threshold with hysteresis, the device returns

to normal operation automatically.

#### 5.2 Application information

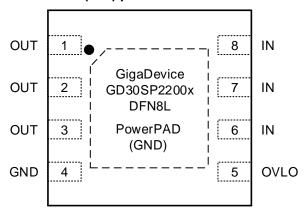

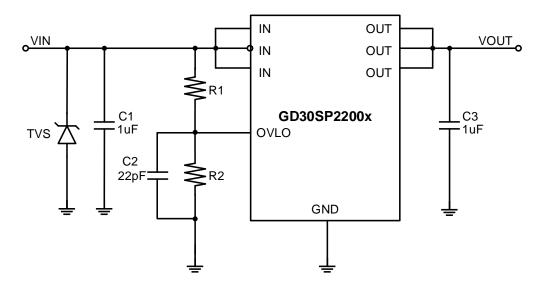

#### 5.2.1 OVLO threshold set up

If OVLO is connected to ground, the internal OVLO comparator uses the internally set OVLO value. Once the OVLO pin voltage exceeds the OVLO select voltage, V<sub>OVLO\_SELECT</sub>, an external resistor divider is used to set the OVLO threshold. By selecting R1 and R2, the OVLO voltage is programmed to the desired value.

$$V_{OVLO} = 1.2 \times (1 + \frac{R_1}{R_2})$$

Figure 5-1 Feedback resistor divider

Note1: R1 and R2 are only required for external ovp, otherwise connect OVLO to GND Note2: Recommend 10K≤R2≤50K; add unidirection TVS close to VIN

#### 5.2.2 Input capacitor selection

A  $1\mu F$  or larger capacitor is typically recommended for  $C_{IN}$ .  $C_{IN}$  should be located close to the device IN pin. Ceramic capacitors are recommended for  $C_{IN}$ . Select capacitors with a voltage rating at least 5V higher than the maximum possible voltage during surge. The 50V- rated capacitors are ideal for most applications.

#### 5.2.3 Output capacitor selection

In order to ensure stability while the current limit is active, a small output capacitance of approximately  $1\mu F$  is required at the output. The output capacitor has no specific capacitor ESR requirement. If desired,  $C_{OUT}$  may be increased to accommodate any load transient condition.

#### 6 Electrical characteristics

#### 6.1 Absolute maximum ratings

The maximum ratings are the limits to which the device can be subjected without permanently damaging the device. Note that the device is not guaranteed to operate properly at the maximum ratings. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

Table 6-1 Absolute maximum ratings

| Symbol            | ymbol Parameter                                 |      | Max     | Unit     |  |

|-------------------|-------------------------------------------------|------|---------|----------|--|

| VIN               | Power supply pin                                |      | 30      | <b>V</b> |  |

| Vouт              | Output                                          | -0.3 | VIN+0.3 | V        |  |

| V <sub>OVLO</sub> | OVLO trip voltage setting                       |      | 17      | V        |  |

| I <sub>IN</sub>   | Continuous current                              |      | 3       | Α        |  |

|                   | Thermal characteristics                         |      |         |          |  |

| TJ                | Operating junction temperature                  |      | 150     | °C       |  |

| T <sub>stg</sub>  | Storage temperature                             |      | 150     | °C       |  |

| P <sub>max</sub>  | Maximum power dissipation @T <sub>A</sub> =25°C |      | 0.5     | W        |  |

#### 6.2 Recommended operation conditions

**Table 6-2 Recommended operation conditions**

| Symbol                  | Symbol Parameter                              |  | Тур | Max | Unit |

|-------------------------|-----------------------------------------------|--|-----|-----|------|

| VIN                     | V <sub>IN</sub> Power supply pin              |  |     | 28  | V    |

| Vovlo                   | VovLo OVLO trip                               |  | _   | 5   | V    |

| Thermal characteristics |                                               |  |     |     |      |

| T <sub>A</sub>          | T <sub>A</sub> Operating ambient temperature  |  | _   | 85  | °C   |

| TJ                      | T <sub>J</sub> Operating junction temperature |  | -   | 125 | °C   |

## 6.3 Electrical sensitivity

The device is strained in order to determine its performance in terms of electrical sensitivity. Electrostatic discharges (ESD) are applied directly to the pins of the sample. Static latch-up (LU) test is based on I-test methods.

Table 6-3 Electrostatic Discharge and Latch-up characteristics

| Symbol    | Parameter                  | Conditions              | Value              | Unit |

|-----------|----------------------------|-------------------------|--------------------|------|

| V         | Electrostatic discharge    | T <sub>A</sub> = 25 °C; | +4000              | \/   |

| VESD(HBM) | voltage (human body model) | JS-001-2017             | ± <del>4</del> 000 | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | T <sub>A</sub> = 25 °C;<br>JS-002-2018 | ±2000 | V  |

|-----------------------|-------------------------------------------------------|----------------------------------------|-------|----|

| Latch up              | I-test                                                | T <sub>A</sub> = 25 °C;<br>JESD78E     | 200   | mA |

## 6.4 Power supplies voltages and currents

Table 6-4 Power supplies voltages and currents

| Symbol              | Parameter                                 | Conditions                                  | Min  | Тур  | Max  | Unit |

|---------------------|-------------------------------------------|---------------------------------------------|------|------|------|------|

| ΙQ                  | Quiescent current                         | $V_{IN} = 5V$ , No switching, $T_J = 25$ °C |      | 100  |      | μΑ   |

| tovp                | OVP Turn-off time                         | VIN > VOVLO, CIN=CL=0pF                     | _    | 450  | _    | ns   |

| Vovlo_th            | Over voltage lockout reference            | _                                           | 1.17 | 1.2  | 1.23 | V    |

| V <sub>OVLO</sub> _ | Over voltage lockout reference hysteresis | _                                           | _    | 35   | _    | mV   |

| Vovlo               | Range of OVLO threshold                   | _                                           | 4    | _    | 15   | V    |

| I <sub>IN</sub>     | Maximum through current                   | _                                           | _    | _    | 3    | Α    |

| Ron                 | Internal switch ON resistance             | V <sub>IN</sub> = 5V, I <sub>OUT</sub> =1A  | _    | 50   | _    | mΩ   |

| ton                 | Turn-on time                              | VIN>VUVLO to VOUT=VIN*90% CL=0              | _    | 16   | _    | ms   |

| V <sub>UVLO</sub>   | VIN under voltage lockout                 | V <sub>IN</sub> rising                      | 1    | 2.25 | 2.37 | ٧    |

| VUVLO<br>_HYS       | VIN under voltage lockout hysteresis      | V <sub>IN</sub> rising to falling threshold | _    | 250  | _    | mV   |

| Vovlo_se<br>lect    | External OVLO select<br>Threshold         | _                                           | _    | 0.25 |      | V    |

#### 6.5 Protections

**Table 6-5 Over temperature characteristics**

| Symbol           | Parameter                    | Conditions          | Min | Тур | Max | Unit |

|------------------|------------------------------|---------------------|-----|-----|-----|------|

| Тот              | Thermal shutdown temperature | Die temperature, TJ | 135 | 150 | 165 | °C   |

| T <sub>HYS</sub> | Thermal hysteresis           | Die temperature, TJ | _   | 20  | _   | °C   |

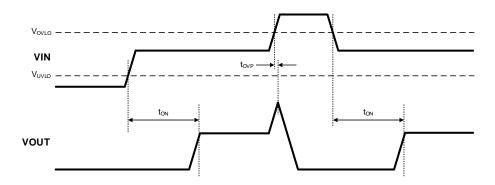

## 6.6 Timing Diagram

Figure 6-1 Timing Diagram

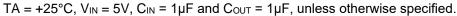

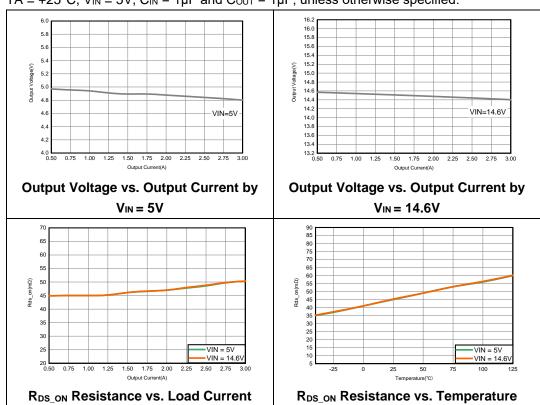

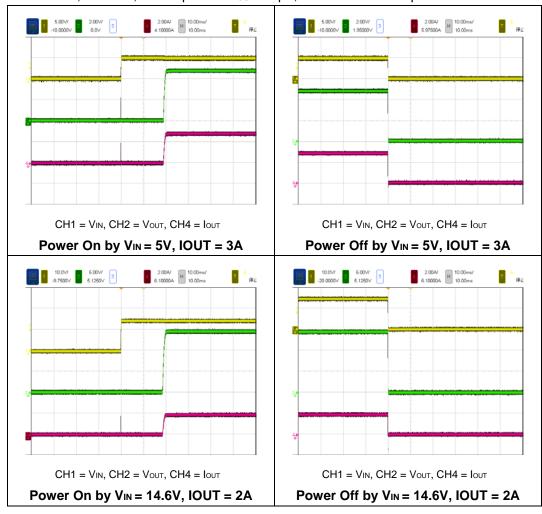

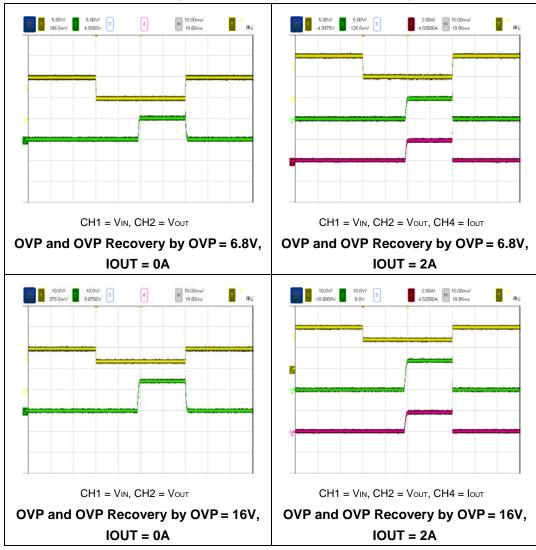

## 6.7 Typical Characteristics

## **Typical Characteristics**

TA = +25°C,  $V_{IN}$  = 5V,  $C_{IN}$  = 1 $\mu$ F and  $C_{OUT}$  = 1 $\mu$ F, unless otherwise specified.

## **Typical Characteristics**

TA = +25°C,  $V_{IN}$  = 5V,  $C_{IN}$  = 1 $\mu$ F and  $C_{OUT}$  = 1 $\mu$ F, unless otherwise specified.

## **Typical Characteristics**

TA = +25°C,  $V_{IN}$  = 5V,  $C_{IN}$  = 1 $\mu$ F and  $C_{OUT}$  = 1 $\mu$ F, unless otherwise specified.

# 7 Typical application circuit

Figure 7-1 Typical GD30SP2200x Application Circuit

The over-voltage protection with external OVLO Threshold setting.

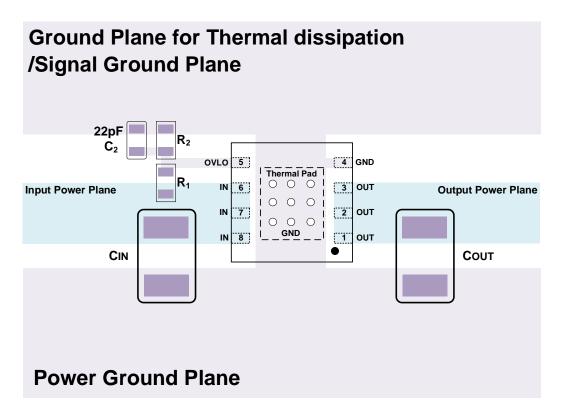

## 8 Layout guideline

To make fully use of the performance of GD30SP2200x, the guidelines below should be followed.

- 1. All the peripherals should be placed as close to the device as possible. Place the input capacitor  $C_{\text{IN}}$  on the top layer (same layer as the GD30SP2200x) and close to IN pin, and place the output capacitor  $C_{\text{OUT}}$  on the top layer(same layer as the GD30SP2200x) and close to OUT pin.

- 2. IN pin routing passes through the external TVS firstly, and then connect GD30SP2200x.

- 3. If R1 and R2 are used, route OVLO line on PCB as short as possible to reduce parasitic capacitance.

# 9 Package information

## 9.1 DFN8L(2X2) package outline dimensions

Figure 9-1 DFN8L(2X2) package outline

Table 9-1 DFN8L(2X2) package dimensions (in mm)

| Symbol | Min  | Тур   | Max  |

|--------|------|-------|------|

| А      | 0.50 | 0.55  | 0.60 |

| A1     | 0    | 0.02  | 0.05 |

| b      | 0.20 | 0.25  | 0.30 |

| b1     | _    | 0.18  | _    |

| С      | _    | 0.152 | _    |

| D      | 1.90 | 2.00  | 2.10 |

| D2     | 1.60 | 1.70  | 1.80 |

| Е      | 1.90 | 2.00  | 2.10 |

| E2     | 0.90 | 1.00  | 1.10 |

| е      | _    | 0.50  | _    |

| h      | 0.20 | 0.25  | 0.30 |

| К      | _    | 0.25  | _    |

| L      | 0.20 | 0.25  | 0.30 |

| Nd     | _    | 1.50  | _    |

Figure 9-2 DFN8L(2X2) recommended footprint

(Original dimensions are in millimeters)

#### 9.2 Thermal characteristics

Thermal resistance is used to characterize the thermal performance of the package device, which is represented by the Greek letter "O". For semiconductor devices, thermal resistance represents the steady-state temperature rise of the chip junction due to the heat dissipated on the chip surface.

Θ<sub>JA</sub>: Thermal resistance, junction-to-ambient.

$\Theta_{JB}$ : Thermal resistance, junction-to-board.

Θ<sub>JC</sub>: Thermal resistance, junction-to-case.

$\Psi_{JB}$ : Thermal characterization parameter, junction-to-board.

Ψ<sub>JT</sub>: Thermal characterization parameter, junction-to-top center.

$\Theta_{JA} = (T_J - T_A)/P_D$

$\Theta_{JB} = (T_J - T_B)/P_D$

$\Theta_{JC} = (T_J - T_C)/P_D$

Where,  $T_J$  = Junction temperature.

$T_A$  = Ambient temperature

T<sub>B</sub> = Board temperature

$T_C$  = Case temperature which is monitoring on package surface

P<sub>D</sub> = Total power dissipation

$\Theta_{JA}$  represents the resistance of the heat flows from the heating junction to ambient air. It is an indicator of package heat dissipation capability. Lower  $\Theta_{JA}$  can be considerate as better overall thermal performance.  $\Theta_{JA}$  is generally used to estimate junction temperature.

$\Theta_{JB}$  is used to measure the heat flow resistance between the chip surface and the PCB board.

$\Theta_{JC}$  represents the thermal resistance between the chip surface and the package top case.  $\Theta_{JC}$  is mainly used to estimate the heat dissipation of the system (using heat sink or other heat dissipation methods outside the device package).

Table 9-2 Package Thermal Characteristics(1)

| Symbol          | Condition                    | Package | Value | Unit |

|-----------------|------------------------------|---------|-------|------|

| $\Theta_{JA}$   | Natural convection, 2S2P PCB | DFN8L   | 86.45 | °C/W |

| ΘЈВ             | Cold plate, 2S2P PCB         | DFN8L   | 36.25 | °C/W |

| Θ <sub>JC</sub> | Cold plate, 2S2P PCB         | DFN8L   | 47.13 | °C/W |

| $\Psi_{JB}$     | Natural convection, 2S2P PCB | DFN8L   | 36.20 | °C/W |

| Ψ <sub>JT</sub> | Natural convection, 2S2P PCB | DFN8L   | 3.61  | °C/W |

<sup>(1)</sup> Thermal characteristics are based on simulation, and meet JEDEC specification.

<sup>(2)</sup> The PCB board is JEDEC standard 2S2P FR-4 PCB board, the PCB Dimension(LXM) 114.3X76.2mm, the PCB thickness 1.6mm, 1oz copper.

<sup>(3)</sup> Power dissipation is calculated by  $P_D = (V_{IN}-V_{OUT}) \times I_{OUT}$ .

# 10 Ordering information

Table 10-1 Part order code for GD30SP2200x devices

| Ordering Code  | Package    | Package Type | Packing Type | MOQ  | Temperature Operating Range  |

|----------------|------------|--------------|--------------|------|------------------------------|

| GD30SP2200WFTR | DFN8L(2X2) | Green        | Tape&Reel    | 3000 | Industrial<br>-40°C to +85°C |

# 11 Revision history

**Table 11-1 Revision history**

| Revision No. | Description     | Date         |

|--------------|-----------------|--------------|

| 1.0          | Initial Release | Aug.15, 2022 |

#### **Important Notice**

This document is the property of GigaDevice Semiconductor Inc. and its subsidiaries (the "Company"). This document, including any product of the Company described in this document (the "Product"), is owned by the Company under the intellectual property laws and treaties of the People's Republic of China and other jurisdictions worldwide. The Company reserves all rights under such laws and treaties and does not grant any license under its patents, copyrights, trademarks, or other intellectual property rights. The names and brands of third party referred thereto (if any) are the property of their respective owner and referred to for identification purposes only.

The Company makes no warranty of any kind, express or implied, with regard to this document or any Product, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. The Company does not assume any liability arising out of the application or use of any Product described in this document. Any information provided in this document is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Except for customized products which has been expressly identified in the applicable agreement, the Products are designed, developed, and/or manufactured for ordinary business, industrial, personal, and/or household applications only. The Products are not designed, intended, or authorized for use as components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, atomic energy control instruments, combustion control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or Product could cause personal injury, death, property or environmental damage ("Unintended Uses"). Customers shall take any and all actions to ensure using and selling the Products in accordance with the applicable laws and regulations. The Company is not liable, in whole or in part, and customers shall and hereby do release the Company as well as its suppliers and/or distributors from any claim, damage, or other liability arising from or related to all Unintended Uses of the Products. Customers shall indemnify and hold the Company as well as it's suppliers and/or distributors harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of the Products.

Information in this document is provided solely in connection with the Products. The Company reserves the right to make changes, corrections, modifications or improvements to this document and Products and services described herein at any time, without notice.

© 2022 GigaDevice - All rights reserved