# GigaDevice Semiconductor Inc.

# GD32A50x Arm® Cortex®-M33 32-bit MCU

For GD32A503xx

## **User Manual**

Revision 1.6

(Feb. 2025)

# **Table of Contents**

| Table o      | of Contents                                                      | 2  |

|--------------|------------------------------------------------------------------|----|

| List of      | Figures                                                          | 16 |

| List of      | Tables                                                           | 22 |

|              | stem and memory architecture                                     |    |

|              |                                                                  |    |

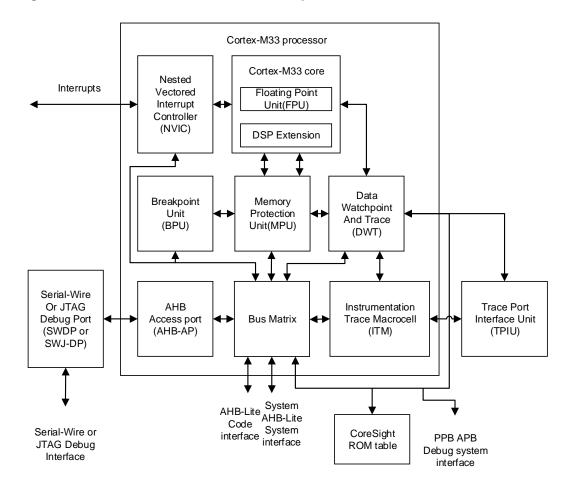

| 1.1.         | Arm® Cortex®-M33 processor                                       |    |

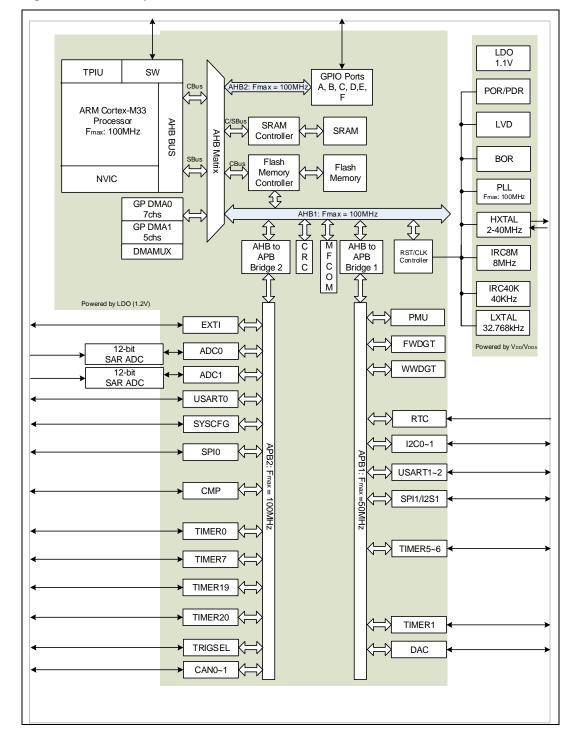

| 1.2.         | System architecture                                              | 26 |

| 1.3.         | Memory map                                                       | 28 |

| 1.3.         | 1. On-chip SRAM memory                                           | 32 |

| 1.3.         | 2. On-chip Flash memory                                          | 34 |

| 1.4.         | Boot configuration                                               | 34 |

| 1.5.         | System configuration controller                                  | 35 |

|              |                                                                  |    |

| 1.6.         | System configuration registers                                   |    |

| 1.6.         | , , , , , , , , , , , , , , , , , , , ,                          |    |

| 1.6.         | , , , , , , , , , , , , , , , , , , , ,                          |    |

| 1.6.         |                                                                  |    |

| 1.6.<br>1.6. |                                                                  |    |

| 1.6.         |                                                                  |    |

| 1.6.         |                                                                  |    |

| 1.6.         |                                                                  |    |

| 1.6.         | - · · · · · · · · · · · · · · · · · · ·                          |    |

| 1.6.         |                                                                  |    |

| 1.7.         | Device electronic signature                                      |    |

| 1.7.         | <del>-</del>                                                     |    |

| 1.7.         |                                                                  |    |

|              | ,                                                                |    |

| 2. Fla       | sh memory controller (FMC)                                       | 50 |

| 2.1.         | Overview                                                         | 50 |

| 2.2.         | Characteristics                                                  | 50 |

| 2.3.         | Function overview                                                | 50 |

| 2.3.         | .1. Flash memory architecture                                    | 50 |

| 2.3.         | .2. Error Checking and Correcting (ECC)                          | 53 |

| 2.3.         | .3. Read operations                                              | 54 |

| 2.3.         | 4. Dual bank architecture with read-while-write (RWW) capability | 55 |

| 2.3.         | .5. Unlock the FMC_CTLx register                                 | 55 |

| 2.3.         | .6. Page erase                                                   | 56 |

|     | 2.3.7.  | Mass erase                                            |      |

|-----|---------|-------------------------------------------------------|------|

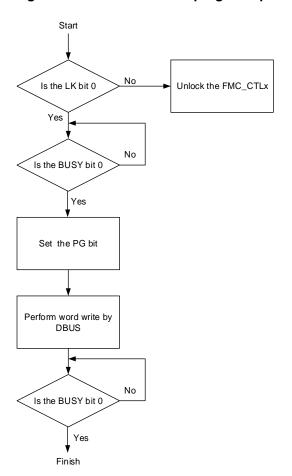

|     | 2.3.8.  | Main flash programming                                |      |

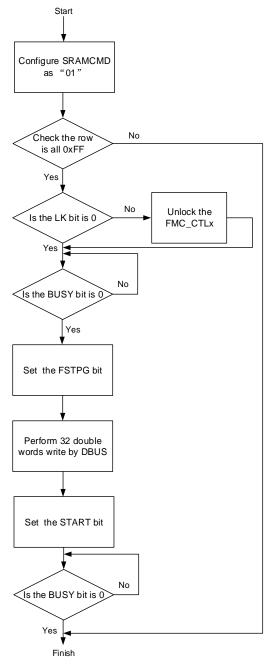

|     | 2.3.9.  | Main Flash Fast Programming                           |      |

| :   | 2.3.10. | Check blank command                                   |      |

|     | 2.3.11. | OTP programming                                       |      |

| :   | 2.3.12. | Shared RAM                                            |      |

| :   | 2.3.13. | Data Flash operation                                  |      |

|     | 2.3.14. | Option bytes 0 erase                                  |      |

| :   | 2.3.15. | Option bytes programming                              | 65   |

| :   | 2.3.16. | Option bytes description                              | 66   |

| :   | 2.3.17. | Erase / program protection                            |      |

| :   | 2.3.18. | Security protection                                   | 70   |

| :   | 2.3.19. | Error description                                     | 71   |

| 2.4 | 4. Rec  | gister definition                                     | 74   |

|     | 2.4.1.  | Wait state register (FMC_WS)                          |      |

|     | 2.4.2.  | ECC control and status register (FMC_ECCCS)           |      |

|     | 2.4.3.  | Unlock key register 0 (FMC_KEY0)                      |      |

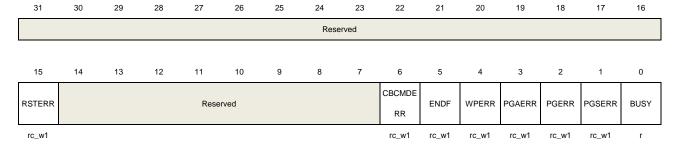

|     | 2.4.4.  | Status register 0 (FMC_STAT0)                         |      |

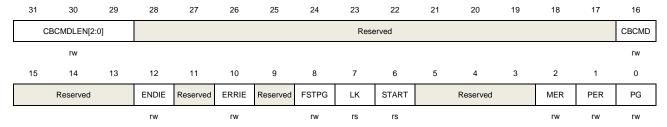

|     | 2.4.5.  | Control register 0 (FMC CTL0)                         |      |

|     | 2.4.6.  | Address register 0 (FMC_ADDR0)                        |      |

| :   | 2.4.7.  | Option byte unlock key register (FMC_OBKEY)           |      |

|     | 2.4.8.  | Unlock key register 1 (FMC_KEY1)                      |      |

|     | 2.4.9.  | Status register 1 (FMC_STAT1)                         |      |

|     | 2.4.10. | Control register 1 (FMC CTL1)                         |      |

|     | 2.4.11. | Address register 1 (FMC_ADDR1)                        |      |

|     | 2.4.12. | Option byte status register (FMC_OBSTAT)              |      |

|     | 2.4.13. | Erase / Program protection register 0 (FMC WP0)       |      |

|     | 2.4.14. | Erase / Program protection register 1 (FMC WP1)       |      |

|     | 2.4.15. | Option byte 1 control and status register (FMC_OB1CS) |      |

|     | 2.4.16. | Product ID register (FMC_PID)                         |      |

|     |         | - , - ,                                               |      |

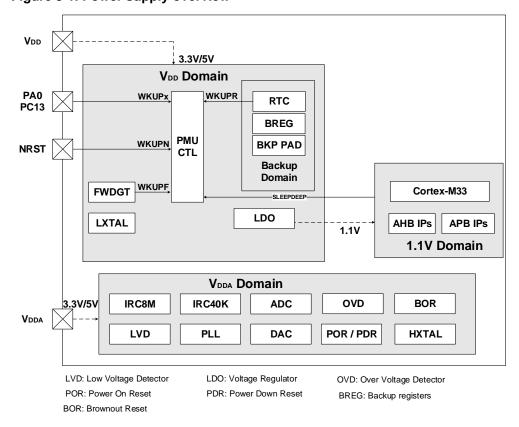

| 3.  | Power   | management unit (PMU)                                 | 88   |

| 3.′ | 1. Ove  | erview                                                | 88   |

| 3.2 | 2. Cha  | racteristics                                          | 88   |

| 3.3 | 3. Fun  | nction overview                                       | . 88 |

|     | 3.3.1.  | V <sub>DD</sub> / V <sub>DDA</sub> power domain       |      |

|     | 3.3.2.  | 1.1V power domain                                     |      |

|     | 3.3.3.  | Power saving modes                                    |      |

|     |         | · ·                                                   |      |

| 3.4 | •       | gister definition                                     |      |

|     | 3.4.1.  | Control register (PMU_CTL)                            |      |

| ;   | 3.4.2.  | Control and status register (PMU_CS)                  | 97   |

| 4.  | Backur  | o registers (BKP)                                     | 100  |

| 4.1  | . C    | Overview                                         | 100 |

|------|--------|--------------------------------------------------|-----|

| 4.2  | . c    | haracteristics                                   | 100 |

| 4.3  | . F    | unction overview                                 | 100 |

| _    | .3.1.  | RTC clock calibration                            |     |

| 4    | .3.2.  | Tamper detection                                 | 100 |

| 4.4  | . F    | legister definition                              | 102 |

| 4    | .4.1.  | Backup data register x (BKP_DATAx) (x= 09)       | 102 |

| 4    | .4.2.  | RTC signal output control register (BKP_OCTL)    | 102 |

| 4    | .4.3.  | Tamper pin control register (BKP_TPCTL)          | 103 |

| 4    | .4.4.  | Tamper control and status register (BKP_TPCS)    | 104 |

| 5. F | Rese   | et and clock unit (RCU)1                         | 106 |

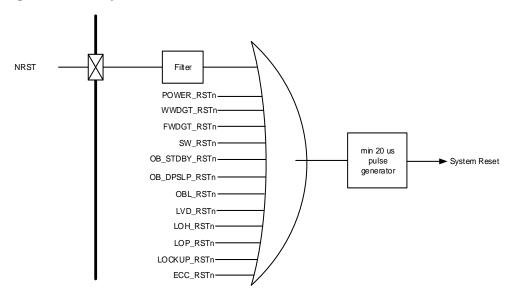

| 5.1  | . F    | eset control unit (RCTL)                         | 106 |

| 5    | 5.1.1. | Overview                                         | 106 |

| 5    | .1.2.  | Function overview                                | 106 |

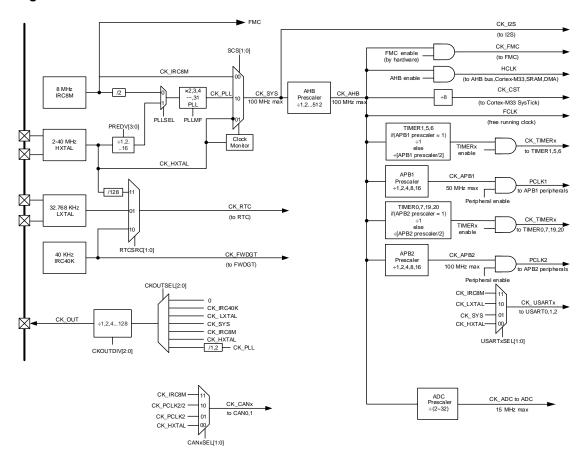

| 5.2  | . c    | clock control unit (CCTL)                        | 107 |

| 5    | 5.2.1. | Overview                                         | 107 |

| 5    | .2.2.  | Characteristics                                  | 109 |

| 5    | .2.3.  | Function overview                                | 109 |

| 5.3  | . F    | egister definition                               | 114 |

| 5    | .3.1.  | Control register (RCU_CTL)                       | 114 |

| 5    | .3.2.  | Configuration register 0 (RCU_CFG0)              | 116 |

| 5    | .3.3.  | Interrupt register (RCU_INT)                     | 119 |

| 5    | .3.4.  | APB2 reset register (RCU_APB2RST)                | 122 |

| 5    | .3.5.  | APB1 reset register (RCU_APB1RST)                | 124 |

| 5    | .3.6.  | AHB enable register (RCU_AHBEN)                  | 126 |

| 5    | .3.7.  | APB2 enable register (RCU_APB2EN)                | 127 |

| 5    | .3.8.  | APB1 enable register (RCU_APB1EN)                | 129 |

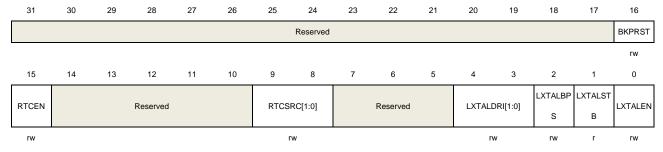

| 5    | .3.9.  | Backup domain control register (RCU_BDCTL)       | 131 |

| 5    | .3.10  | Reset source /clock register (RCU_RSTSCK)        | 132 |

| 5    | .3.11  | . AHB reset register (RCU_AHBRST)                | 135 |

| 5    | .3.12  | Configuration register 1 (RCU_CFG1)              | 137 |

| 5    | .3.13  |                                                  |     |

| 5    | .3.14  |                                                  |     |

| 5    | .3.15  | Deep-sleep mode voltage register (RCU_DSV)       | 140 |

| 6. l | nter   | rupt / event controller (EXTI)1                  | 141 |

| 6.1  | . (    | )verview                                         | 141 |

| 6.2  | . 0    | characteristics                                  | 141 |

| 6.3  | . lı   | nterrupts function overview                      | 141 |

| 6.4  | . Е    | xternal interrupt and event (EXTI) block diagram | 145 |

| 6.5.   | External Interrupt and Event function overview                           | 145 |

|--------|--------------------------------------------------------------------------|-----|

| 6.6.   | Register definition                                                      | 148 |

| 6.6    | .1. Interrupt enable register (EXTI_INTEN)                               | 148 |

| 6.6    | .2. Event enable register (EXTI_EVEN)                                    | 148 |

| 6.6    | .3. Rising edge trigger enable register (EXTI_RTEN)                      | 149 |

| 6.6    | .4. Falling edge trigger enable register (EXTI_FTEN)                     | 149 |

| 6.6    | .5. Software interrupt event register (EXTI_SWIEV)                       | 149 |

| 6.6    | .6. Pending register (EXTI_PD)                                           | 150 |

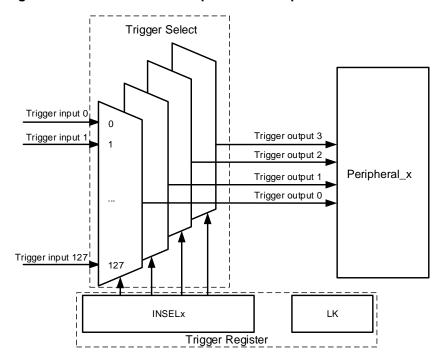

| 7. Tri | gger selection controller (TRIGSEL)                                      | 151 |

| 7.1.   | Overview                                                                 | 151 |

| 7.2.   | Characteristics                                                          | 151 |

| 7.3.   | Function overview                                                        | 151 |

| 7.4.   | Internal connect                                                         | 152 |

| 7.5.   | Register definition                                                      | 157 |

| 7.5    | <b>G</b>                                                                 |     |

| 7.5    |                                                                          |     |

| 7.5    | .3. Trigger selection for ADC0 register (TRIGSEL_ADC0)                   | 159 |

| 7.5    | .4. Trigger selection for ADC1 register (TRIGSEL_ADC1)                   | 159 |

| 7.5    | .5. Trigger selection for DAC register (TRIGSEL_DAC)                     | 160 |

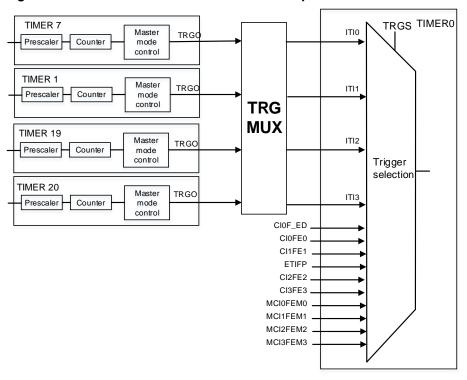

| 7.5    | .6. Trigger selection for TIMER0_ITI register (TRIGSEL_TIMER0IN)         | 160 |

| 7.5    | .7. Trigger selection for TIMER0_BRKIN register (TRIGSEL_TIMER0BRKIN)    | 161 |

| 7.5    | .8. Trigger selection for TIMER7_ITI register (TRIGSEL_TIMER7IN)         | 162 |

| 7.5    | .9. Trigger selection for TIMER7_BRKIN register (TRIGSEL_TIMER7BRKIN)    | 163 |

| 7.5    | .10. Trigger selection for TIMER19_ITI register (TRIGSEL_TIMER19IN)      | 164 |

| 7.5    | .11. Trigger selection for TIMER19_BRKIN register (TRIGSEL_TIMER19BRKIN) | 165 |

| 7.5    | .12. Trigger selection for TIMER20_ITI register (TRIGSEL_TIMER20IN)      | 166 |

| 7.5    | .13. Trigger selection for TIMER20_BRKIN register (TRIGSEL_TIMER20BRKIN) | 167 |

| 7.5    | .14. Trigger selection for TIMER1_ITI register (TRIGSEL_TIMER1IN)        | 168 |

| 7.5    | .15. Trigger selection for MFCOM register (TRIGSEL_MFCOM)                | 169 |

| 7.5    | .16. Trigger selection for CAN0 register (TRIGSEL_CAN0)                  | 170 |

| 7.5    | .17. Trigger selection for CAN1 register (TRIGSEL_CAN1)                  | 171 |

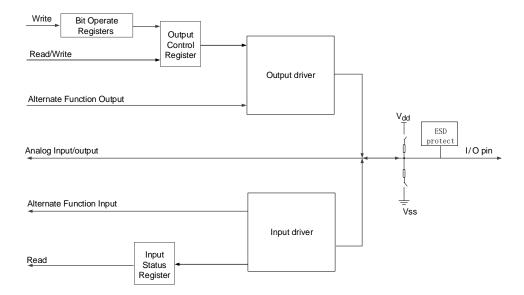

| 8. Ge  | eneral-purpose and alternate-function I/Os (GPIO and AFIO)               | 172 |

| 8.1.   | Overview                                                                 | 172 |

| 8.2.   | Characteristics                                                          | 172 |

| 8.3.   | Function overview                                                        | 172 |

| 8.3    |                                                                          |     |

| 8.3    | .2. External interrupt/event lines                                       | 174 |

| 8.3    | .3. Alternate functions (AF)                                             | 174 |

| 8.3    | .4. Additional functions                                                 | 174 |

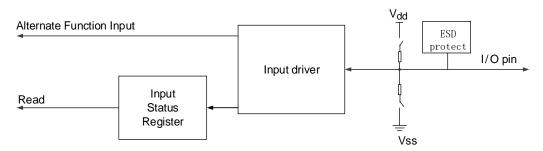

| 8.3    | .5. Input configuration                                                  | 175 |

# GD32A50x User Manual

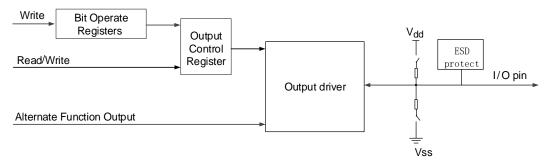

| 8.3.6.    | Output configuration                                        | 175 |

|-----------|-------------------------------------------------------------|-----|

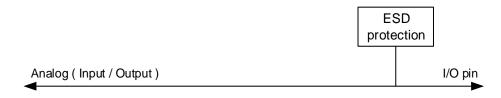

| 8.3.7.    | Analog configuration                                        | 176 |

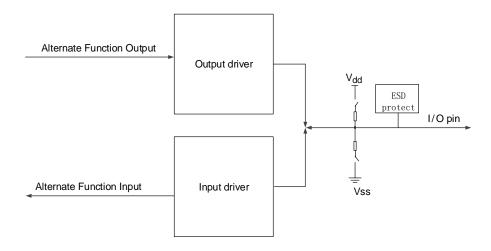

| 8.3.8.    | Alternate function (AF) configuration                       | 176 |

| 8.3.9.    | GPIO locking function                                       | 177 |

| 8.3.10.   | GPIO single cycle toggle function                           | 177 |

| 8.4. Re   | egister definition                                          | 178 |

| 8.4.1.    | Port control register (GPIOx_CTL, x=AF)                     |     |

| 8.4.2.    | Port output mode register (GPIOx_OMODE, x=AF)               | 180 |

| 8.4.3.    | Port output speed register (GPIOx_OSPD, x=AF)               | 181 |

| 8.4.4.    | Port pull-up/down register (GPIOx_PUD, x=AF)                | 183 |

| 8.4.5.    | Port input status register (GPIOx_ISTAT, x=AF)              | 185 |

| 8.4.6.    | Port output control register (GPIOx_OCTL, x=AF)             | 185 |

| 8.4.7.    | Port bit operate register (GPIOx_BOP, x=AF)                 | 185 |

| 8.4.8.    | Port configuration lock register (GPIOx_LOCK, x=AF)         | 186 |

| 8.4.9.    | Alternate function selected register 0 (GPIOx_AFSEL0, x=AF) | 187 |

| 8.4.10.   | Alternate function selected register 1 (GPIOx_AFSEL1, x=AF) | 188 |

| 8.4.11.   | Bit clear register (GPIOx_BC, x=AF)                         | 189 |

| 8.4.12.   | Port bit toggle register (GPIOx_TG, x=AF)                   | 190 |

| 9. Multi- | function communication Interface (MFCOM)                    | 191 |

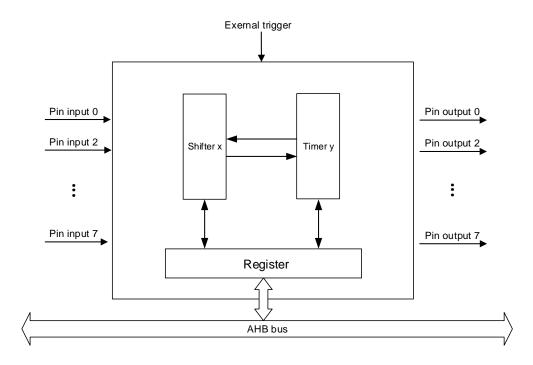

| 9.1. Ov   | verview                                                     | 191 |

|           | naracteristics                                              | 101 |

|           |                                                             |     |

| 9.3. Bl   | ock diagram                                                 | 191 |

| 9.4. Fu   | ınction overview                                            | 192 |

| 9.4.1.    | Clocking and resets                                         | 192 |

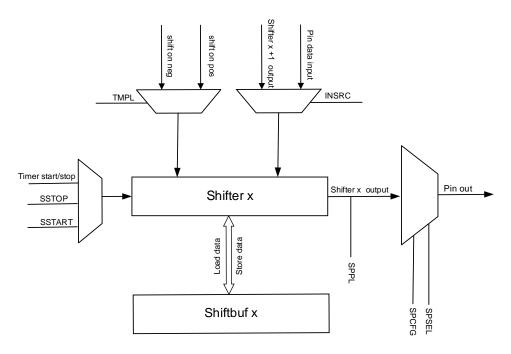

| 9.4.2.    | Shifter                                                     | 192 |

| 9.4.3.    | Timer                                                       | 193 |

| 9.4.4.    | Pin                                                         | 196 |

| 9.4.5.    | Interrupts and DMA requests                                 | 197 |

| 9.4.6.    | Triggers                                                    | 197 |

| 9.5. Re   | egister definition                                          | 198 |

| 9.5.1.    | Control register (MFCOM_CTL)                                | 198 |

| 9.5.2.    | Pin data register (MFCOM_PINDATA)                           | 198 |

| 9.5.3.    | Shifter status register (MFCOM_SSTAT)                       | 199 |

| 9.5.4.    | Shifter error register (MFCOM_SERR)                         | 199 |

| 9.5.5.    | Timer status register (MFCOM_TMSTAT)                        | 200 |

| 9.5.6.    | Shifter status interrupt enable register (MFCOM_SSIEN)      | 200 |

| 9.5.7.    | Shifter error interrupt enable register (MFCOM_SEIEN)       | 201 |

| 9.5.8.    | Timer status interrupt enable register (MFCOM_TMSIEN)       | 201 |

| 9.5.9.    | Shifter status DMA enable register (MFCOM_SSDMAEN)          | 202 |

| 9.5.10.   | Shifter control x register (MFCOM_SCTLx)                    | 202 |

| 9.5.11.   | Shifter configuration x register (MFCOM_SCFGx)              | 204 |

| 9.5.12  | 2. Shifter buffer x register (MFCOM_SBUFx)                     | 205 |

|---------|----------------------------------------------------------------|-----|

| 9.5.13  | Shifter buffer x bit swapped register (MFCOM_SBUFBISx)         | 205 |

| 9.5.14  | Shifter buffer x byte swapped register (MFCOM_SBUFBYSx)        | 206 |

| 9.5.15  | 5. Shifter buffer x bit byte swapped register (MFCOM_SBUFBBSx) | 206 |

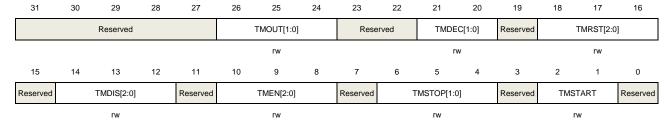

| 9.5.16  | 5. Timer control x register (MFCOM_TMCTLx)                     | 206 |

| 9.5.17  | '. Timer configuration x register (MFCOM_TMCFGx)               | 208 |

| 9.5.18  | B. Timer compare x register (MFCOM_TMCMPx)                     | 210 |

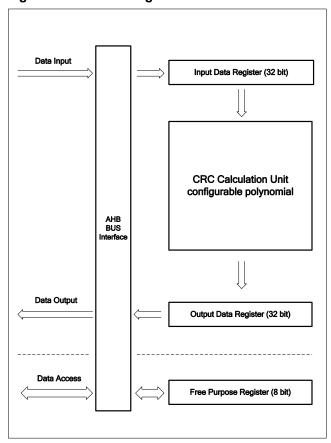

| 10. CR  | C calculation unit (CRC)                                       | 212 |

| 10.1.   | Overview                                                       | 212 |

| 10.2.   | Characteristics                                                | 212 |

| 10.3.   | Function overview                                              | 213 |

| 10.4.   | Register definition                                            | 214 |

| 10.4.1  | Data register (CRC_DATA)                                       | 214 |

| 10.4.2  | P. Free data register (CRC_FDATA)                              | 214 |

| 10.4.3  | 8. Control register (CRC_CTL)                                  | 215 |

| 10.4.4  | Initialization data register (CRC_IDATA)                       | 215 |

| 10.4.5  | 5. Polynomial register (CRC_POLY)                              | 216 |

| 11. Dir | ect memory access controller (DMA)                             | 217 |

| 11.1.   | Overview                                                       | 217 |

| 11.2.   | Characteristics                                                | 217 |

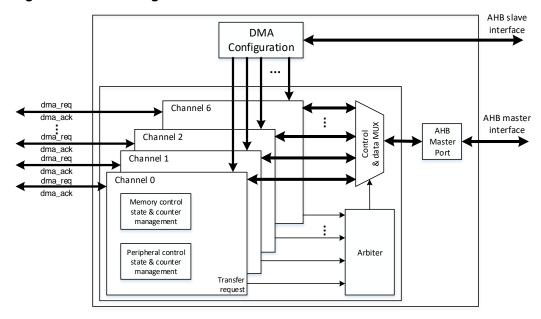

| 11.3.   | Block diagram                                                  | 218 |

| 11.4.   | Function overview                                              | 218 |

| 11.4.1  | . DMA operation                                                | 218 |

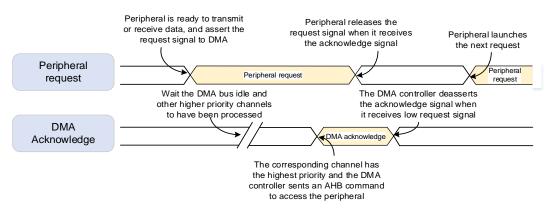

| 11.4.2  | Peripheral handshake                                           | 220 |

| 11.4.3  | . Arbitration                                                  | 221 |

| 11.4.4  | Address generation                                             | 221 |

| 11.4.5  | Circular mode                                                  | 221 |

| 11.4.6  | . Memory to memory mode                                        | 221 |

| 11.4.7  | Channel configuration                                          | 221 |

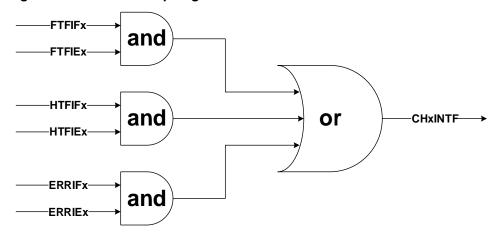

| 11.4.8  | . Interrupt                                                    | 222 |

| 11.4.9  | DMA request mapping                                            | 223 |

| 11.5.   | Register definition                                            | 224 |

| 11.5.1  | . Interrupt flag register (DMA_INTF)                           | 224 |

| 11.5.2  | . Interrupt flag clear register (DMA_INTC)                     | 225 |

| 11.5.3  | Channel x control register (DMA_CHxCTL)                        | 225 |

| 11.5.4  | . Channel x counter register (DMA_CHxCNT)                      | 227 |

| 11.5.5  | . Channel x peripheral base address register (DMA_CHxPADDR)    | 228 |

| 11.5.6  | Channel x memory base address register (DMA_CHxMADDR)          | 228 |

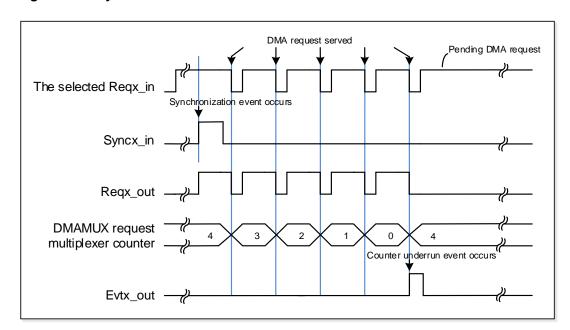

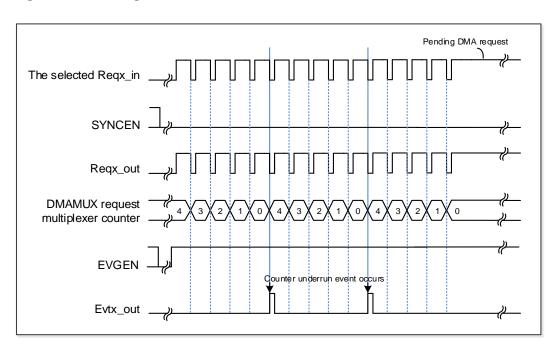

| 12. DN  | IA request multiplexer (DMAMUX)                                | 230 |

| 12.1.  | Overview                                                                      | 230 |

|--------|-------------------------------------------------------------------------------|-----|

| 12.2.  | Characteristics                                                               | 230 |

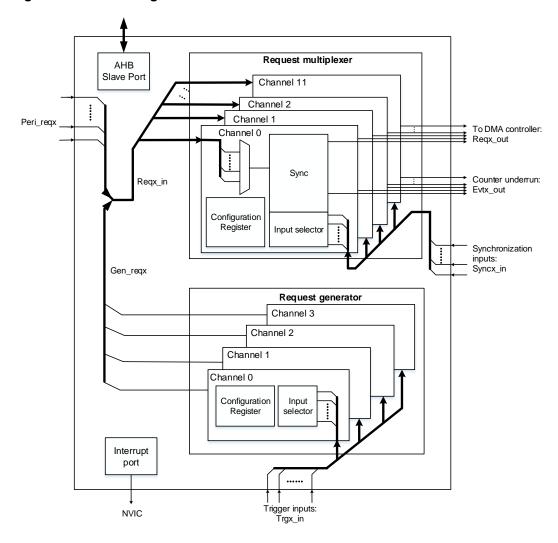

| 12.3.  | Block diagram                                                                 | 231 |

| 12.4.  | Function overview                                                             |     |

| 12.4.  |                                                                               |     |

| 12.4.2 |                                                                               |     |

| 12.4.3 | ·                                                                             |     |

| 12.4.4 |                                                                               |     |

| 12.4.5 | •                                                                             |     |

| 12.4.6 | 6. DMAMUX mapping                                                             | 236 |

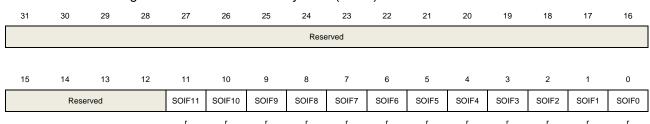

| 12.5.  | Register definition                                                           | 241 |

| 12.5.  | Request multiplexer channel x configuration register (DMAMUX_RM_CHxCFG)       | 241 |

| 12.5.2 | 2. Request multiplexer channel interrupt flag register (DMAMUX_RM_INTF)       | 242 |

| 12.5.3 | 3. Request multiplexer channel interrupt flag clear register (DMAMUX_RM_INTC) | 242 |

| 12.5.4 | 4. Request generator channel x configuration register (DMAMUX_RG_CHxCFG)      | 243 |

| 12.5.5 | 5. Request generator interrupt flag register (DMAMUX_RG_INTF)                 | 244 |

| 12.5.6 | 6. Request generator interrupt flag clear register (DMAMUX_RG_INTC)           | 244 |

| 13. De | bug (DBG)                                                                     | 246 |

| 13.1.  | Introduction                                                                  |     |

| 13.2.  | JTAG/SW function overview                                                     | 246 |

| 13.2.  |                                                                               |     |

| 13.2.2 |                                                                               |     |

| 13.2.3 | · ·                                                                           |     |

| 13.2.4 | •                                                                             |     |

| 13.2.5 | 5. JEDEC-106 ID code                                                          | 247 |

| 13.3   | Debug hold function overview                                                  | 247 |

| 13.3.  |                                                                               |     |

| 13.3.2 |                                                                               |     |

|        |                                                                               |     |

| 13.4.  | Registers definition                                                          |     |

| 13.4.1 | 1. ID code register (DBG_ID)<br>2. Control register (DBG_CTL)                 |     |

|        |                                                                               |     |

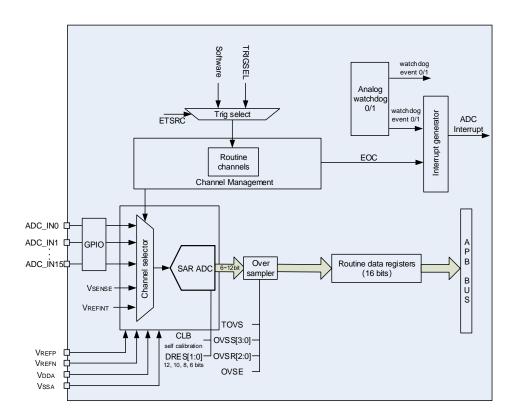

| 14. An | alog-to-digital converter (ADC)                                               |     |

| 14.1.  | Overview                                                                      | 252 |

| 14.2.  | Characteristics                                                               | 252 |

| 14.3.  | Pins and internal signals                                                     | 253 |

| 14.4.  | Function overview                                                             | 254 |

| 14.4.  |                                                                               |     |

|        | 2. ADC clock                                                                  |     |

| 14.4.3.  | ADC enable                                          | 255 |

|----------|-----------------------------------------------------|-----|

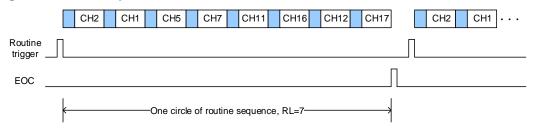

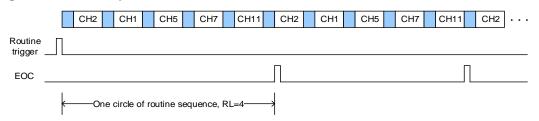

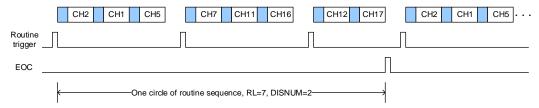

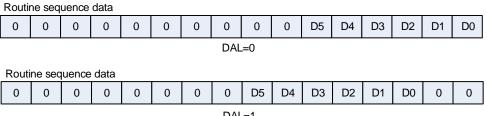

| 14.4.4.  | Routine sequence                                    | 255 |

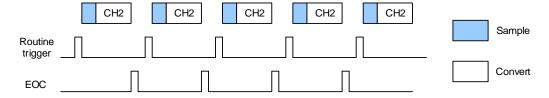

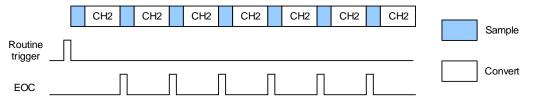

| 14.4.5.  | Operation modes                                     | 255 |

| 14.4.6.  | Conversion result threshold monitor                 | 258 |

| 14.4.7.  | Data storage mode                                   | 259 |

| 14.4.8.  | Sample time configuration                           | 259 |

| 14.4.9.  | External trigger configuration                      | 260 |

| 14.4.10  | DMA request                                         | 260 |

| 14.4.11. | ADC internal channels                               | 260 |

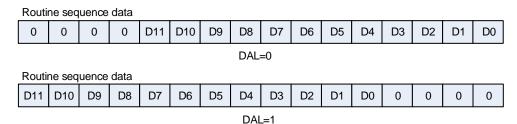

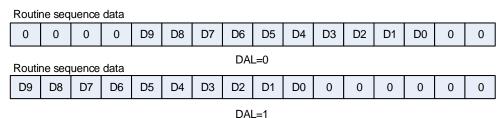

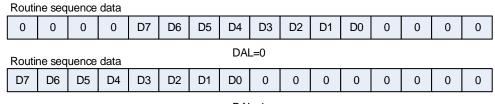

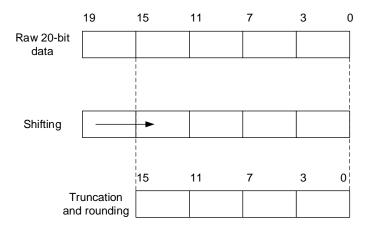

| 14.4.12  | Programmable resolution (DRES)                      | 261 |

| 14.4.13  | . On-chip hardware oversampling                     | 262 |

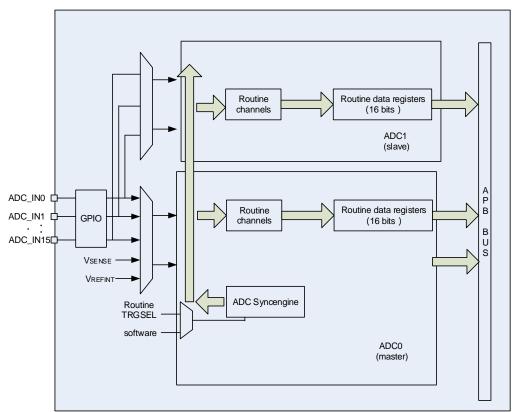

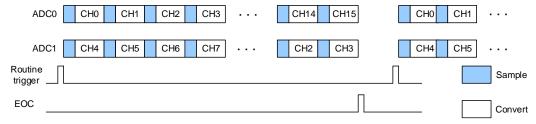

| 14.5.    | ADC sync mode                                       | 263 |

| 14.5.1.  | Free mode                                           | 264 |

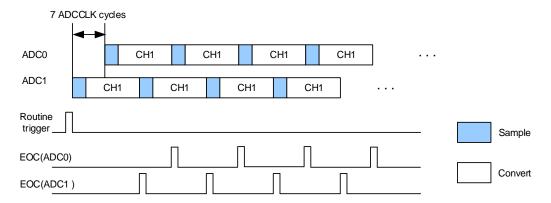

| 14.5.2.  | Routine parallel mode                               | 265 |

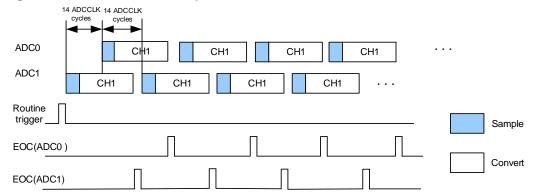

| 14.5.3.  | Routine follow-up fast mode                         | 265 |

| 14.5.4.  | Routine follow-up slow mode                         | 266 |

| 14.6.    | ADC interrupts                                      | 267 |

| 14.7. I  | Register definition                                 | 268 |

| 14.7.1.  | Status register (ADC_STAT)                          |     |

| 14.7.2.  | Control register 0 (ADC_CTL0)                       |     |

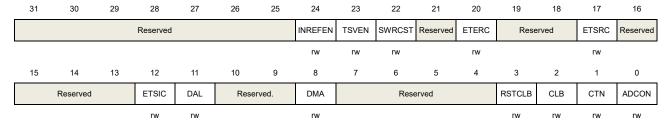

| 14.7.3.  | Control register 1 (ADC_CTL1)                       | 271 |

| 14.7.4.  | Sample time register 0 (ADC_SAMPT0)                 | 272 |

| 14.7.5.  | Sample time register 1 (ADC_SAMPT1)                 | 273 |

| 14.7.6.  | Watchdog high threshold register 0 (ADC_WDHT0)      | 274 |

| 14.7.7.  | Watchdog low threshold register 0 (ADC_WDLT0)       | 274 |

| 14.7.8.  | Routine sequence register 0 (ADC_RSQ0)              | 275 |

| 14.7.9.  | Routine sequence register 1 (ADC_RSQ1)              | 275 |

| 14.7.10  | . Routine sequence register 2 (ADC_RSQ2)            | 276 |

| 14.7.11. | Routine data register (ADC_RDATA)                   | 277 |

| 14.7.12  | . Oversample control register (ADC_OVSAMPCTL)       | 277 |

| 14.7.13  | . Watchdog 1 channel selection register (ADC_WD1SR) | 279 |

| 14.7.14  | . Watchdog threshold register 1 (ADC_WDT1)          | 279 |

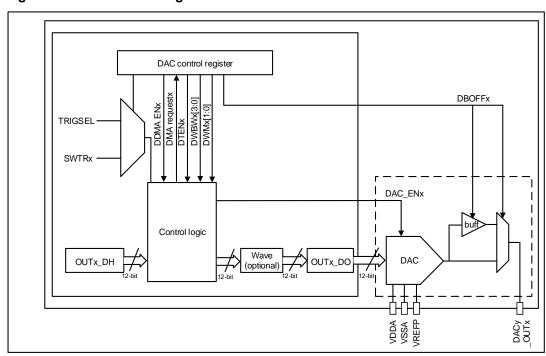

| 15. Digi | tal-to-analog converter (DAC)                       | 281 |

| 15.1.    | Overview                                            | 281 |

| 15.2.    | Characteristics                                     | 281 |

| 15.3. I  | Function overview                                   | 282 |

| 15.3.1.  | DAC enable                                          |     |

| 15.3.2.  | DAC output buffer                                   |     |

| 15.3.3.  | DAC data configuration                              |     |

| 15.3.4.  | DAC trigger                                         |     |

| 15.3.5.  | DAC conversion                                      | 283 |

# GD32A50x User Manual

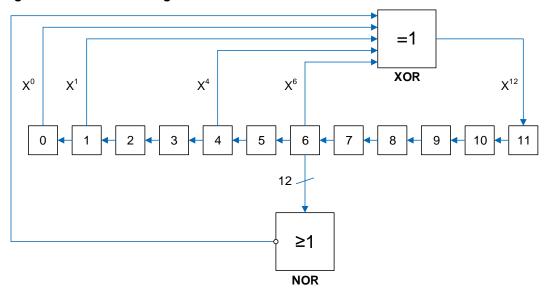

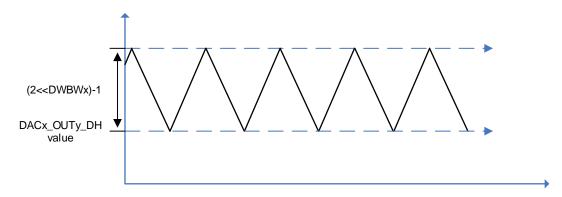

| 15.3.6                   | DAC noise wave                                                       | 283 |

|--------------------------|----------------------------------------------------------------------|-----|

| 15.3.7                   | DAC output voltage                                                   | 284 |

| 15.3.8                   | DMA request                                                          | 284 |

| 15.4.                    | Register definition                                                  | 286 |

| 15.4.1.                  | •                                                                    |     |

| 15.4.2                   |                                                                      |     |

| 15.4.3                   |                                                                      |     |

| 15.4.4                   | DACx_OUT0 12-bit left-aligned data holding register (DAC_OUT0_L12DH) | 288 |

| 15.4.5                   | DACx_OUT0 8-bit right-aligned data holding register (DAC_OUT0_R8DH)  | 289 |

| 15.4.6                   | DACx_OUT0 data output register (DAC_OUT0_DO)                         | 289 |

| 15.4.7                   | DACx status register 0 (DAC_STAT0)                                   | 290 |

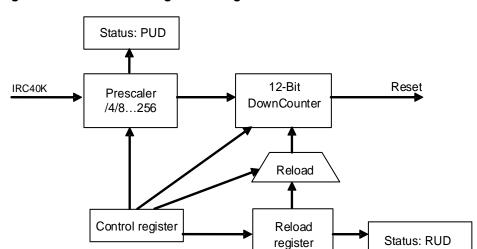

| 16. Wa                   | tchdog timer (WDGT)                                                  | 291 |

| 16.1.                    | Free watchdog timer (FWDGT)                                          | 291 |

| 16.1.1.                  | <b>5</b> ,                                                           |     |

| 16.1.2                   |                                                                      |     |

| 16.1.3                   | Function overview                                                    | 291 |

| 16.1.4                   | Register definition                                                  | 294 |

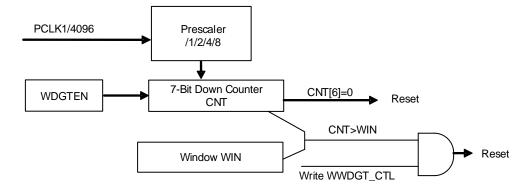

| 16.2.                    | Window watchdog timer (WWDGT)                                        | 298 |

| 16.2.1.                  | • ,                                                                  |     |

| 16.2.2.                  | Characteristics                                                      | 298 |

| 16.2.3                   | Function overview                                                    | 298 |

| 16.2.4                   | Register definition                                                  | 301 |

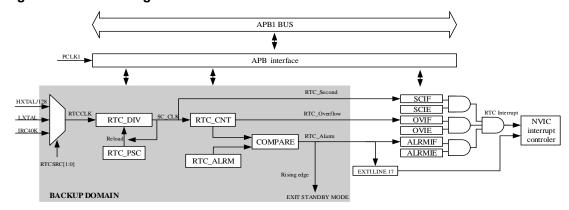

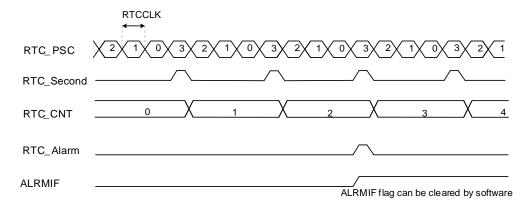

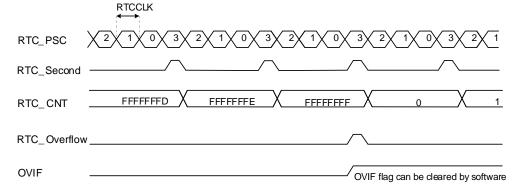

| 17. Rea                  | al-time clock (RTC)                                                  | 303 |

| 17.1.                    | Overview                                                             | 303 |

| 17.2.                    | Characteristics                                                      | 303 |

| 17.3.                    | Function overview                                                    |     |

| 17. <b>3.</b><br>17.3.1. |                                                                      |     |

| 17.3.1.                  |                                                                      |     |

| 17.3.3                   | <u> </u>                                                             |     |

| 17.3.4                   | •                                                                    |     |

| 17.4.                    | Register definition                                                  | 307 |

| 17.4.1.                  |                                                                      |     |

| 17.4.2.                  |                                                                      |     |

| 17.4.3                   |                                                                      |     |

| 17.4.4.                  |                                                                      |     |

| 17.4.5                   | · · · · · · · · · · · · · · · · · · ·                                |     |

| 17.4.6                   |                                                                      |     |

| 17.4.7                   | - · · · - · · · · · · · · · · · · · · ·                              |     |

| 17.4.8                   | RTC counter low register (RTC_CNTL)                                  | 310 |

| 17.4.9                   | RTC alarm high register (RTC_ALRMH)                                  | 311 |

| 17.4.10                                                                                                                                                      | . RTC alarm low register (RTC_ALRML)                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 311                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| 18. TIM                                                                                                                                                      | ER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 312                                                     |

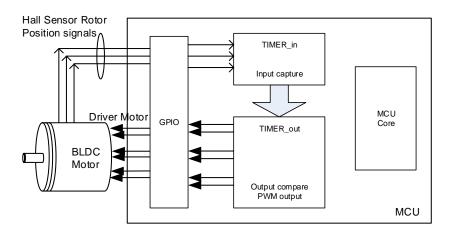

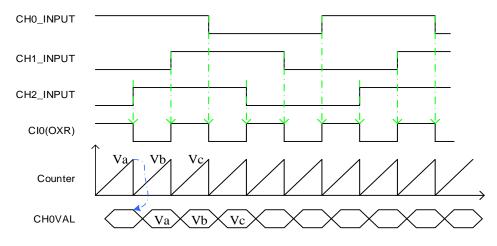

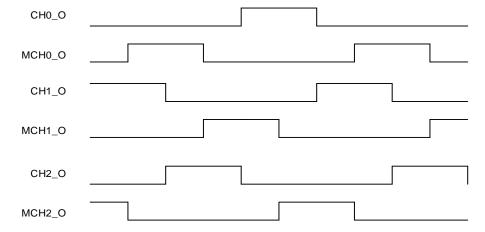

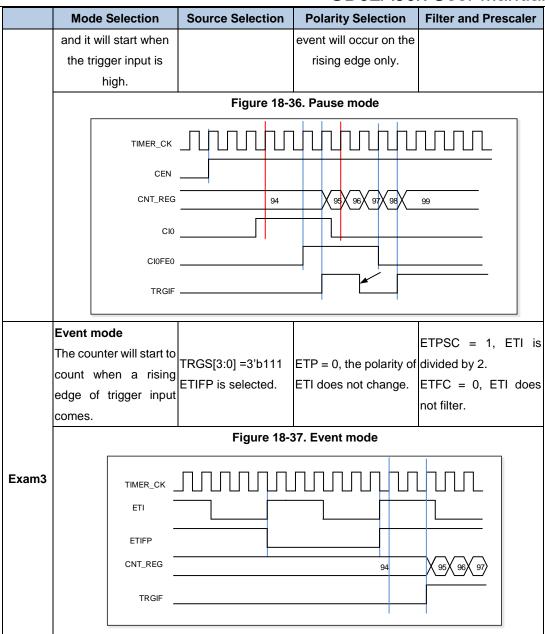

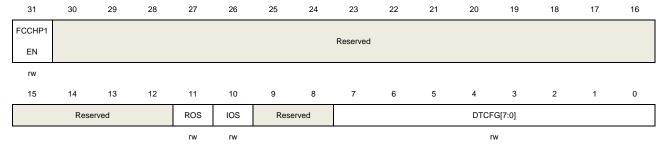

| 18.1.                                                                                                                                                        | Advanced timer (TIMERx, x=0, 7, 19, 20)                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 313                                                     |

| 18.1.1.                                                                                                                                                      | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                         |

| 18.1.2.                                                                                                                                                      | Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 313                                                     |

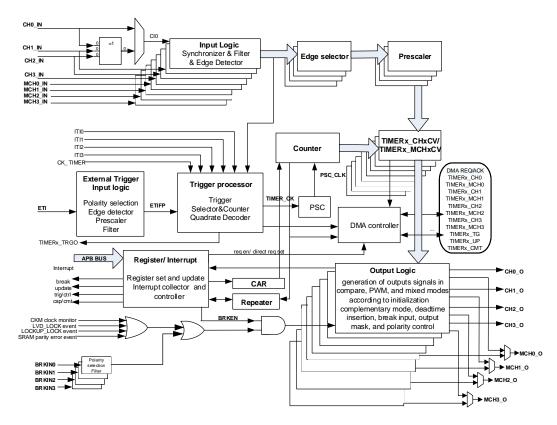

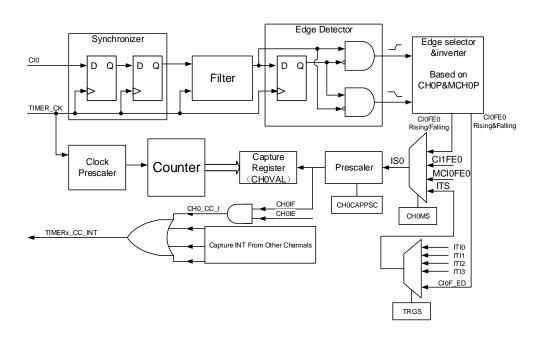

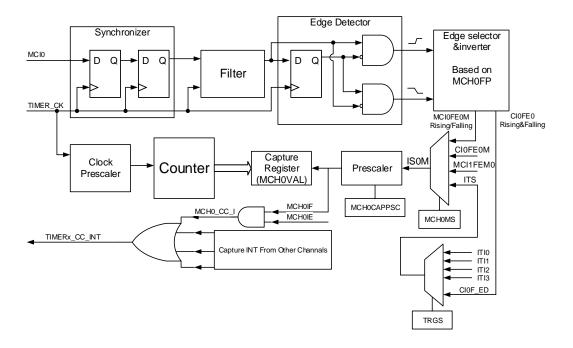

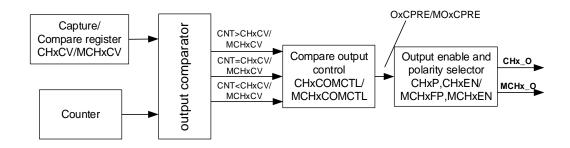

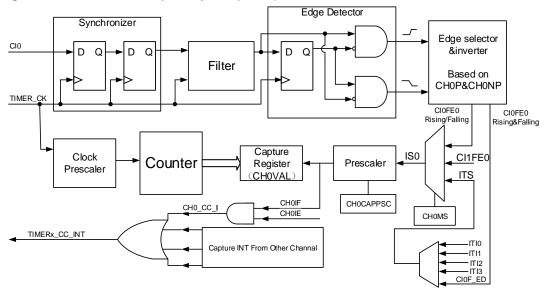

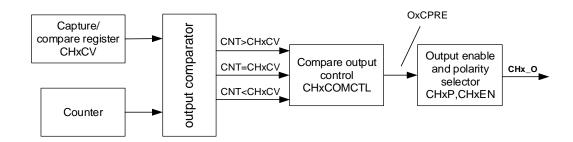

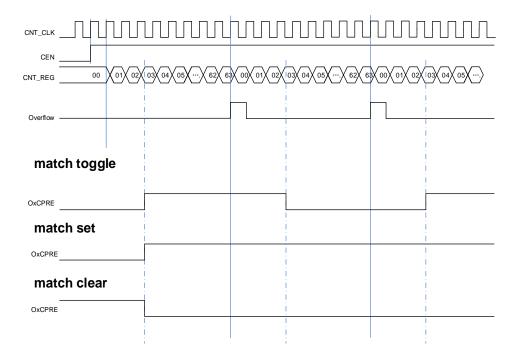

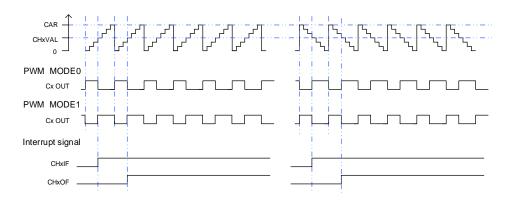

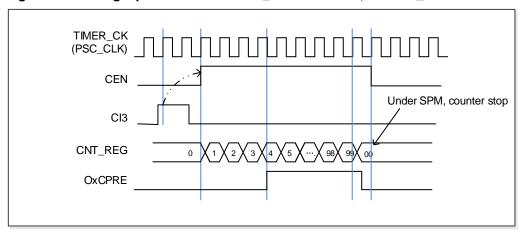

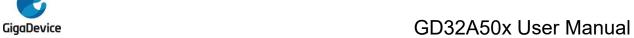

| 18.1.3.                                                                                                                                                      | Block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 314                                                     |

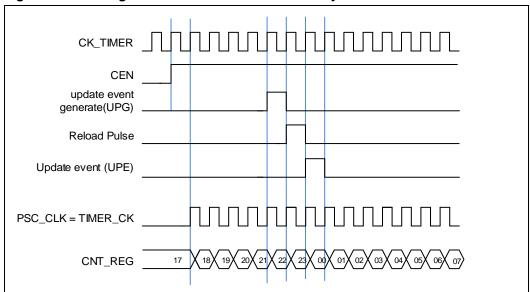

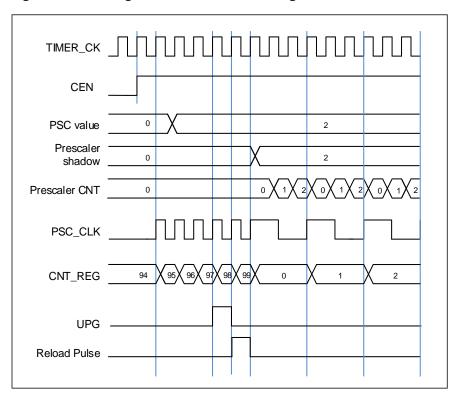

| 18.1.4.                                                                                                                                                      | Function overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 314                                                     |

| 18.1.5.                                                                                                                                                      | Registers definition (TIMERx, x=0, 7, 19, 20)                                                                                                                                                                                                                                                                                                                                                                                                                                            | 349                                                     |

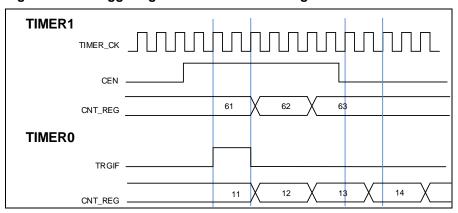

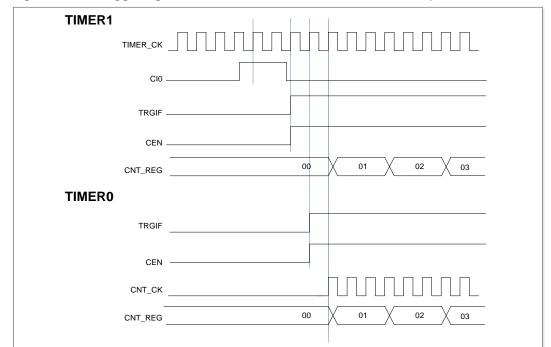

| 18.2.                                                                                                                                                        | General level0 timer (TIMERx, x=1)                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 407                                                     |

| 18.2.1.                                                                                                                                                      | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 407                                                     |

| 18.2.2.                                                                                                                                                      | Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 407                                                     |

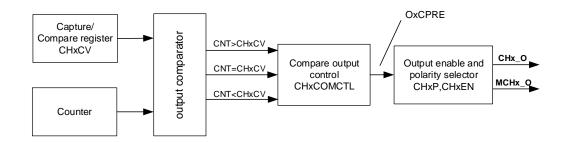

| 18.2.3.                                                                                                                                                      | Block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 407                                                     |

| 18.2.4.                                                                                                                                                      | Function overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 408                                                     |

| 18.2.5.                                                                                                                                                      | Registers definition (TIMERx, x=1)                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 424                                                     |

| 18.3.                                                                                                                                                        | Basic timer (TIMERx, x=5, 6)                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 447                                                     |

| 18.3.1.                                                                                                                                                      | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 447                                                     |

| 18.3.2.                                                                                                                                                      | Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 447                                                     |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 447                                                     |

| 18.3.3.                                                                                                                                                      | Block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                         |

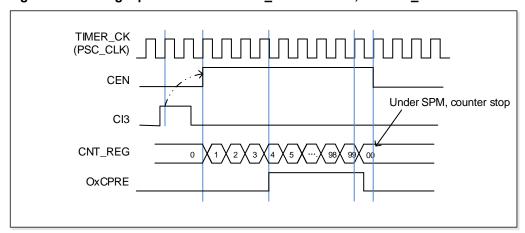

| 18.3.3.<br>18.3.4.                                                                                                                                           | Block diagram Function overview                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                         |

|                                                                                                                                                              | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 447                                                     |

| 18.3.4.<br>18.3.5.                                                                                                                                           | Function overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 447<br>451                                              |

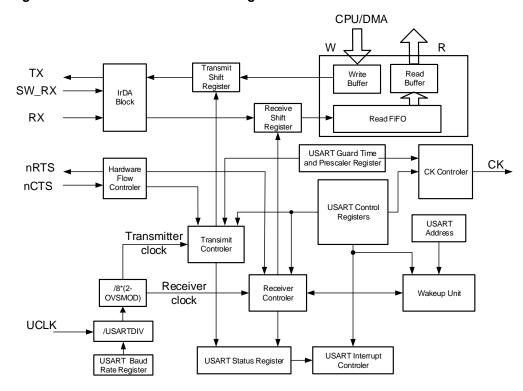

| 18.3.4.<br>18.3.5.<br><b>19. Uni</b> v                                                                                                                       | Function overview  Registers definition (TIMERx, x=5, 6)  /ersal synchronous/asynchronous receiver /transmitter (USART)                                                                                                                                                                                                                                                                                                                                                                  | 447<br>451                                              |

| 18.3.4.<br>18.3.5.<br><b>19. Univ</b>                                                                                                                        | Function overviewRegisters definition (TIMERx, x=5, 6)  versal synchronous/asynchronous receiver /transmitter (USART)  Overview                                                                                                                                                                                                                                                                                                                                                          | 447<br>451<br><b>456</b>                                |

| 18.3.4.<br>18.3.5.<br><b>19. Univ</b><br><b>19.1.</b><br><b>19.2.</b>                                                                                        | Function overviewRegisters definition (TIMERx, x=5, 6)  versal synchronous/asynchronous receiver /transmitter (USART)  Overview                                                                                                                                                                                                                                                                                                                                                          | 447 451 456 456                                         |

| 18.3.4.<br>18.3.5.<br>19. Univ<br>19.1.<br>19.2.                                                                                                             | Function overview  Registers definition (TIMERx, x=5, 6)  Versal synchronous/asynchronous receiver /transmitter (USART)  Overview  Characteristics  Function overview                                                                                                                                                                                                                                                                                                                    | 447 451 456 456                                         |

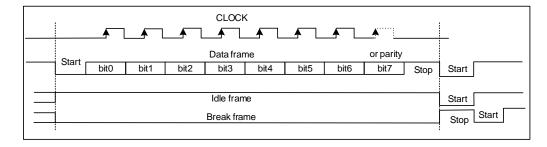

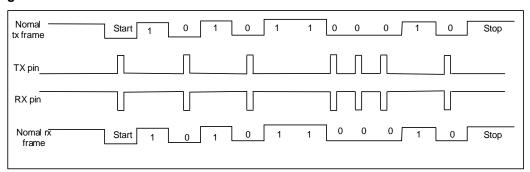

| 18.3.4.<br>18.3.5.<br><b>19. Univ</b><br><b>19.1.</b><br><b>19.2.</b>                                                                                        | Function overview  Registers definition (TIMERx, x=5, 6)  Versal synchronous/asynchronous receiver /transmitter (USART)  Overview  Characteristics  Function overview  USART frame format                                                                                                                                                                                                                                                                                                | 447 456 456 456 456                                     |

| 18.3.4.<br>18.3.5.<br>19. Univ<br>19.1.<br>19.2.<br>19.3.<br>19.3.1.<br>19.3.2.                                                                              | Function overview  Registers definition (TIMERx, x=5, 6)  Versal synchronous/asynchronous receiver /transmitter (USART)  Overview  Characteristics  Function overview  USART frame format  Baud rate generation                                                                                                                                                                                                                                                                          | 447 456 456 456 456 457 458                             |

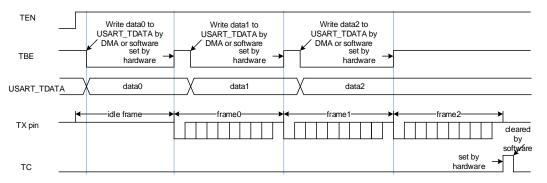

| 18.3.4.<br>18.3.5.<br><b>19. Univ</b><br><b>19.1.</b><br><b>19.2.</b><br><b>19.3.</b><br>19.3.1.<br>19.3.2.<br>19.3.3.                                       | Function overview  Registers definition (TIMERx, x=5, 6)  Versal synchronous/asynchronous receiver /transmitter (USART)  Overview  Characteristics  Function overview  USART frame format  Baud rate generation  USART transmitter.                                                                                                                                                                                                                                                      | 447 456 456 456 458 458 460                             |

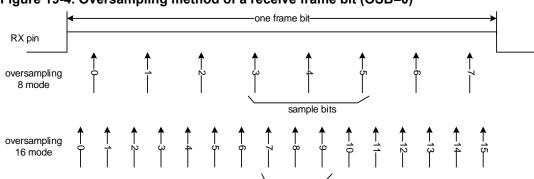

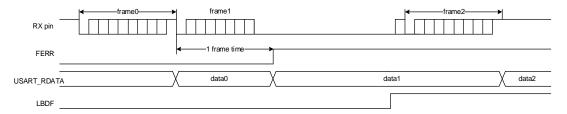

| 18.3.4.<br>18.3.5.<br>19. Univ<br>19.1.<br>19.2.<br>19.3.<br>19.3.1.<br>19.3.2.<br>19.3.3.<br>19.3.4.                                                        | Function overview Registers definition (TIMERx, x=5, 6)  Versal synchronous/asynchronous receiver /transmitter (USART)  Overview  Characteristics  Function overview  USART frame format  Baud rate generation  USART transmitter  USART receiver                                                                                                                                                                                                                                        | 447 456 456 456 457 458 460 461                         |

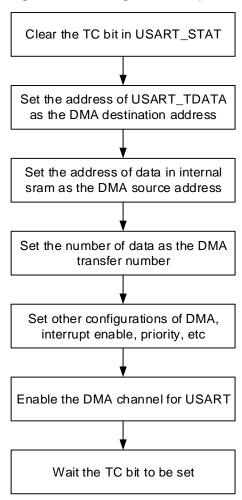

| 18.3.4.<br>18.3.5.<br><b>19. Univ</b><br><b>19.1.</b><br><b>19.2.</b><br><b>19.3.</b><br>19.3.1.<br>19.3.2.<br>19.3.3.<br>19.3.4.<br>19.3.5.                 | Function overview Registers definition (TIMERx, x=5, 6)  Versal synchronous/asynchronous receiver /transmitter (USART)  Overview  Characteristics  Function overview  USART frame format  Baud rate generation  USART transmitter  USART receiver  USART receiver  Use DMA for data buffer access                                                                                                                                                                                        | 447 456 456 456 457 458 460 462                         |

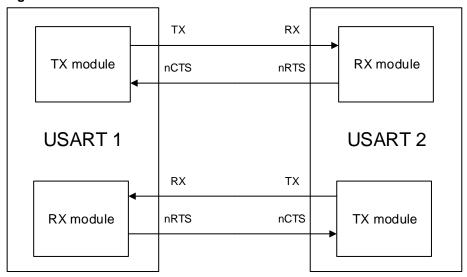

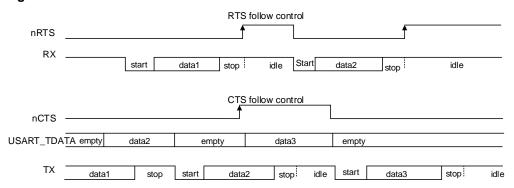

| 18.3.4.<br>18.3.5.<br>19. Univ<br>19.1.<br>19.2.<br>19.3.<br>19.3.1.<br>19.3.2.<br>19.3.3.<br>19.3.4.                                                        | Function overview  Registers definition (TIMERx, x=5, 6)  Versal synchronous/asynchronous receiver /transmitter (USART)  Overview  Characteristics  USART frame format  Baud rate generation  USART transmitter  USART receiver  USART receiver  Use DMA for data buffer access  Hardware flow control                                                                                                                                                                                   | 447 456 456 456 458 469 461 464                         |

| 18.3.4.<br>18.3.5.<br><b>19. Univ</b><br><b>19.1.</b><br><b>19.2.</b><br><b>19.3.</b><br>19.3.1.<br>19.3.2.<br>19.3.3.<br>19.3.4.<br>19.3.5.                 | Function overview Registers definition (TIMERx, x=5, 6)                                                                                                                                                                                                                                                                                                                                                                                                                                  | 447 456 456 456 456 466 462 465                         |

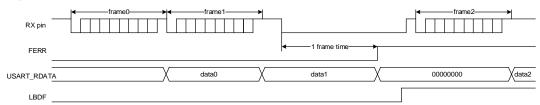

| 18.3.4.<br>18.3.5.<br>19. Univ<br>19.1.<br>19.2.<br>19.3.1.<br>19.3.2.<br>19.3.3.<br>19.3.4.<br>19.3.5.<br>19.3.6.                                           | Function overview Registers definition (TIMERx, x=5, 6)  Versal synchronous/asynchronous receiver /transmitter (USART)  Overview  Characteristics  Function overview  USART frame format  Baud rate generation  USART transmitter  USART receiver  USART receiver  Use DMA for data buffer access  Hardware flow control  Multi-processor communication  LIN mode                                                                                                                        | 447 456 456 456 456 458 461 464 465 466                 |

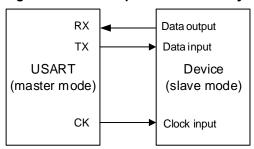

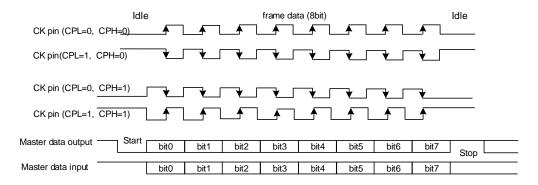

| 18.3.4. 18.3.5.  19. Univ  19.1. 19.2. 19.3. 19.3.1. 19.3.2. 19.3.3. 19.3.4. 19.3.5. 19.3.6. 19.3.7. 19.3.8. 19.3.9.                                         | Function overview Registers definition (TIMERx, x=5, 6)  Versal synchronous/asynchronous receiver /transmitter (USART)  Overview Characteristics  Function overview USART frame format Baud rate generation USART transmitter. USART receiver Use DMA for data buffer access Hardware flow control Multi-processor communication LIN mode Synchronous mode.                                                                                                                              | 447 456 456 456 457 462 465 465 467                     |

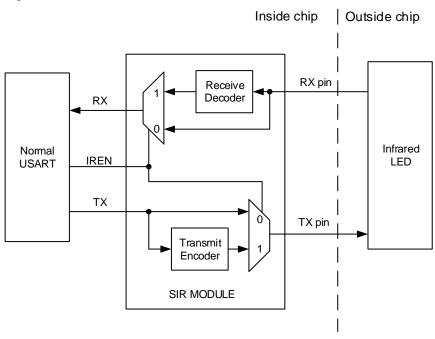

| 18.3.4. 18.3.5.  19. Univ  19.1. 19.2. 19.3.1. 19.3.2. 19.3.3. 19.3.4. 19.3.5. 19.3.6. 19.3.7. 19.3.8. 19.3.9. 19.3.10                                       | Function overview Registers definition (TIMERx, x=5, 6)  Versal synchronous/asynchronous receiver /transmitter (USART)  Overview  Characteristics  Function overview  USART frame format  Baud rate generation  USART transmitter  USART receiver  Use DMA for data buffer access  Hardware flow control  Multi-processor communication  LIN mode  Synchronous mode  IrDA SIR ENDEC mode                                                                                                 | 447 456 456 456 456 458 461 464 466 466 468             |

| 18.3.4. 18.3.5.  19. Univ  19.1. 19.2. 19.3. 19.3.1. 19.3.2. 19.3.3. 19.3.4. 19.3.5. 19.3.6. 19.3.7. 19.3.8. 19.3.9. 19.3.10 19.3.11                         | Function overview Registers definition (TIMERx, x=5, 6)  Versal synchronous/asynchronous receiver /transmitter (USART)  Overview  Characteristics  Function overview  USART frame format  Baud rate generation  USART transmitter  USART receiver  Use DMA for data buffer access  Hardware flow control  Multi-processor communication  LIN mode  Synchronous mode  IrDA SIR ENDEC mode  Half-duplex communication mode                                                                 | 447 456 456 456 456 457 466 467 468 468                 |

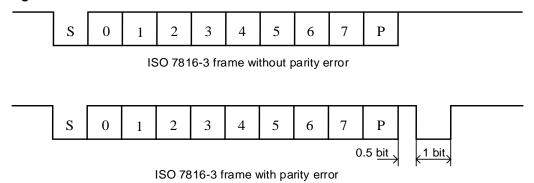

| 18.3.4. 18.3.5.  19. Univ  19.1. 19.2. 19.3. 19.3.1. 19.3.2. 19.3.3. 19.3.4. 19.3.5. 19.3.6. 19.3.7. 19.3.8. 19.3.9. 19.3.10 19.3.11 19.3.12                 | Function overview Registers definition (TIMERx, x=5, 6)  Versal synchronous/asynchronous receiver /transmitter (USART)  Overview  Characteristics  Function overview  USART frame format  Baud rate generation  USART transmitter  USART receiver  USE DMA for data buffer access  Hardware flow control  Multi-processor communication  LIN mode  Synchronous mode  IrDA SIR ENDEC mode  Half-duplex communication mode  Smartcard (ISO7816-3) mode                                     | 447 456 456 456 456 458 461 462 466 468 468 470         |

| 18.3.4. 18.3.5.  19. Univ  19.1. 19.2. 19.3. 19.3.1. 19.3.2. 19.3.3. 19.3.4. 19.3.5. 19.3.6. 19.3.7. 19.3.8. 19.3.9. 19.3.10 19.3.11 19.3.12 19.3.13         | Function overview Registers definition (TIMERx, x=5, 6)  // Versal synchronous/asynchronous receiver /transmitter (USART)  // Overview  Characteristics  Function overview  USART frame format  Baud rate generation  USART transmitter  USART receiver  Use DMA for data buffer access  Hardware flow control  Multi-processor communication  LIN mode  Synchronous mode  IrDA SIR ENDEC mode  Half-duplex communication mode  Smartcard (ISO7816-3) mode  ModBus communication         | 447 456 456 456 456 457 467 468 467 470 472             |

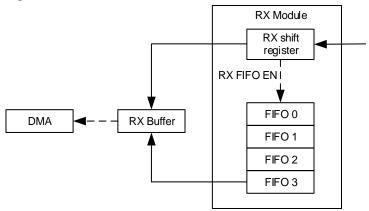

| 18.3.4. 18.3.5.  19. Univ  19.1. 19.2. 19.3. 19.3.1. 19.3.2. 19.3.3. 19.3.4. 19.3.5. 19.3.6. 19.3.7. 19.3.8. 19.3.9. 19.3.10 19.3.11 19.3.12 19.3.13 19.3.14 | Function overview Registers definition (TIMERx, x=5, 6)  Versal synchronous/asynchronous receiver /transmitter (USART)  Overview  Characteristics  Function overview  USART frame format  Baud rate generation  USART transmitter  USART receiver  Use DMA for data buffer access  Hardware flow control  Multi-processor communication  LIN mode  Synchronous mode  IrDA SIR ENDEC mode  Half-duplex communication mode  Smartcard (ISO7816-3) mode  ModBus communication  Receive FIFO | 447 456 456 456 456 458 461 462 464 466 467 470 472 472 |

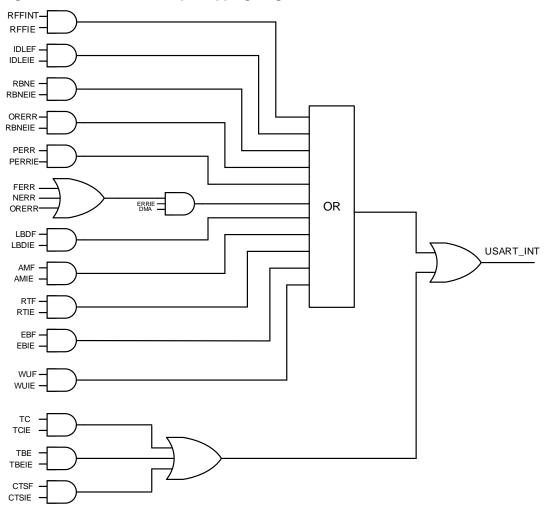

| 18.3.4. 18.3.5.  19. Univ  19.1. 19.2. 19.3. 19.3.1. 19.3.2. 19.3.3. 19.3.4. 19.3.5. 19.3.6. 19.3.7. 19.3.8. 19.3.9. 19.3.10 19.3.11 19.3.12 19.3.13 19.3.14 | Function overview Registers definition (TIMERx, x=5, 6)  // Versal synchronous/asynchronous receiver /transmitter (USART)  // Overview  Characteristics  Function overview  USART frame format  Baud rate generation  USART transmitter  USART receiver  Use DMA for data buffer access  Hardware flow control  Multi-processor communication  LIN mode  Synchronous mode  IrDA SIR ENDEC mode  Half-duplex communication mode  Smartcard (ISO7816-3) mode  ModBus communication         | 447 456 456 456 456 458 461 462 464 466 467 470 472 472 |

| 19.4. F   | legister definition                                         | 476 |

|-----------|-------------------------------------------------------------|-----|

| 19.4.1.   | Control register 0 (USART_CTL0)                             | 476 |

| 19.4.2.   | Control register 1 (USART_CTL1)                             | 478 |

| 19.4.3.   | Control register 2 (USART_CTL2)                             | 481 |

| 19.4.4.   | Baud rate generator register (USART_BAUD)                   | 483 |

| 19.4.5.   | Prescaler and guard time configuration register (USART_GP)  | 484 |

| 19.4.6.   | Receiver timeout register (USART_RT)                        | 485 |

| 19.4.7.   | Command register (USART_CMD)                                | 486 |

| 19.4.8.   | Status register (USART_STAT)                                | 486 |

| 19.4.9.   | Interrupt status clear register (USART_INTC)                | 490 |

| 19.4.10.  | Receive data register (USART_RDATA)                         | 491 |

| 19.4.11.  | Transmit data register (USART_TDATA)                        | 492 |

| 19.4.12.  | USART coherence control register (USART_CHC)                | 492 |

| 19.4.13.  | USART receive FIFO control and status register (USART_RFCS) | 493 |

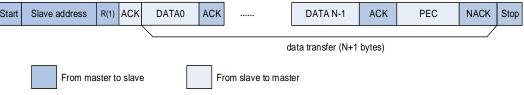

| 20. Inter | -integrated circuit interface (I2C)                         | 495 |

|           |                                                             |     |

| 20.1. C   | Overview                                                    | 495 |

| 20.2. C   | characteristics                                             | 495 |

| 20.3. F   | unction overview                                            | 495 |

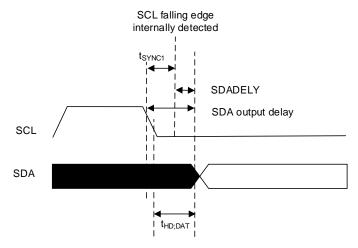

| 20.3.1.   | Clock requirements                                          |     |

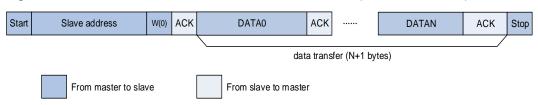

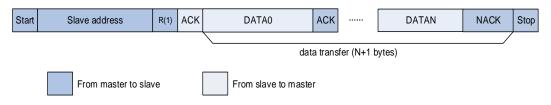

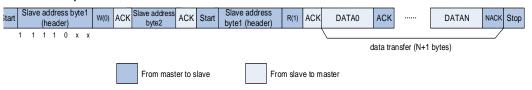

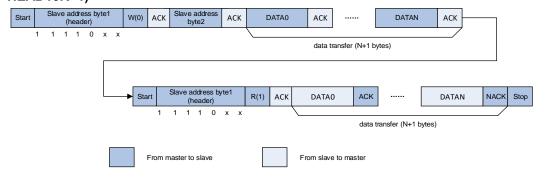

| 20.3.2.   | I2C communication flow                                      |     |

| 20.3.3.   | Noise filter                                                |     |

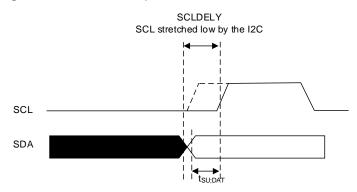

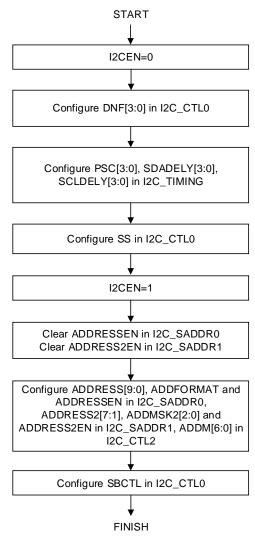

| 20.3.4.   | I2C timings configuration                                   | 500 |

| 20.3.5.   | I2C reset                                                   |     |

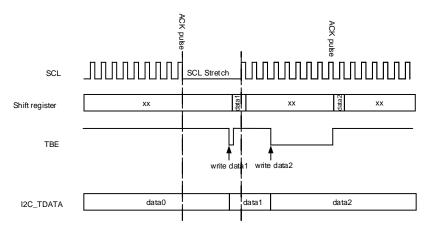

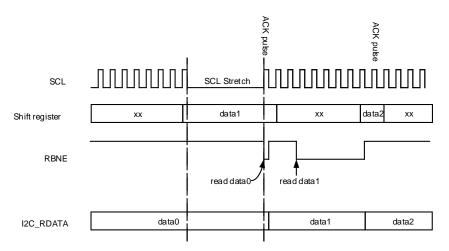

| 20.3.6.   | Data transfer                                               | 502 |

| 20.3.7.   | I2C slave mode                                              | 504 |

| 20.3.8.   | I2C master mode                                             | 509 |

| 20.3.9.   | SMBus support                                               | 514 |

| 20.3.10.  | SMBus mode                                                  | 517 |

| 20.3.11.  | Use DMA for data transfer                                   | 519 |

| 20.3.12.  | I2C error and interrupts                                    | 519 |

| 20.3.13.  | I2C debug mode                                              | 520 |

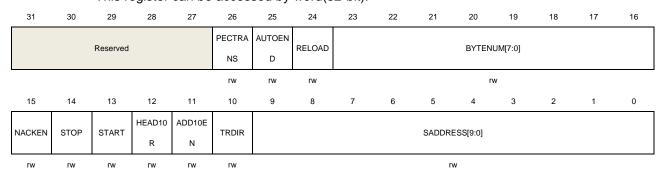

| 20.4. F   | legister definition                                         | 521 |

| 20.4.1.   | Control register 0 (I2C_CTL0)                               |     |

| 20.4.2.   | Control register 1 (I2C_CTL1)                               |     |

| 20.4.3.   | Slave address register 0 (I2C_SADDR0)                       |     |

| 20.4.4.   | Slave address register 1 (I2C_SADDR1)                       |     |

| 20.4.5.   | Timing register (I2C_TIMING)                                |     |

| 20.4.6.   | Timeout register (I2C_TIMEOUT)                              |     |

| 20.4.7.   | Status register (I2C_STAT)                                  |     |

| 20.4.8.   | Status clear register (I2C_STATC)                           |     |

| 20.4.9.   | PEC register (I2C_PEC)                                      |     |

|           | Receive data register (I2C_RDATA)                           |     |

|           | · · · · · · · · · · · · · · · · · · ·                       |     |

| 20.4.1       | Transmit data register (I2C_TDATA)                   | 533 |

|--------------|------------------------------------------------------|-----|

| 20.4.12      | 2. Control register 2 (I2C_CTL2)                     | 534 |

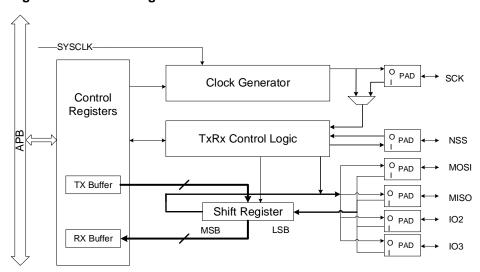

| 21. Ser      | ial peripheral interface/Inter-IC sound (SPI/I2S)    | 535 |

| 21.1.        | Overview                                             | 535 |

| 21.2.        | Characteristics                                      | 535 |

| 21.2.1.      | SPI characteristics                                  | 535 |

| 21.2.2.      | I2S characteristics                                  | 535 |

| 21.3.        | SPI function overview                                | 536 |

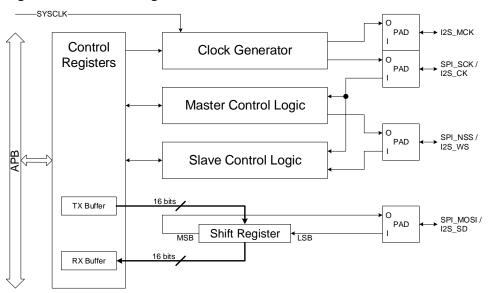

| 21.3.1.      | SPI block diagram                                    | 536 |

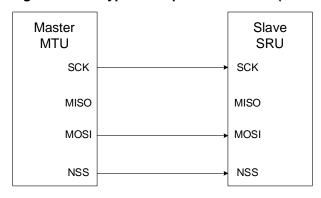

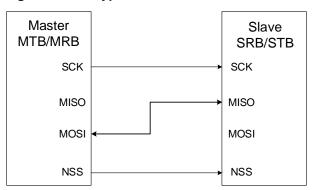

| 21.3.2.      | SPI signal description                               | 536 |

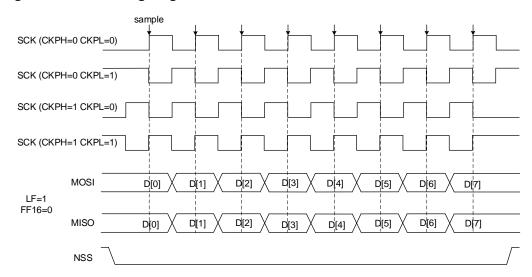

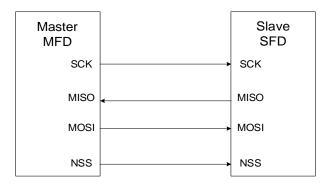

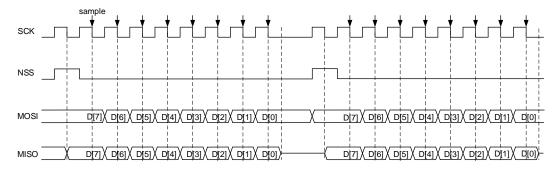

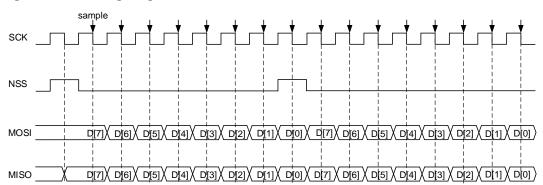

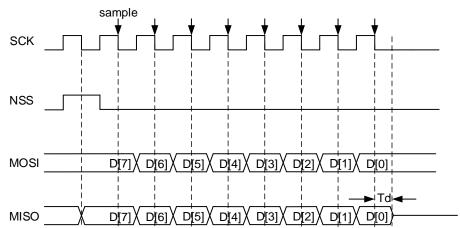

| 21.3.3.      | SPI clock timing and data format                     | 537 |

| 21.3.4.      | NSS function                                         | 538 |

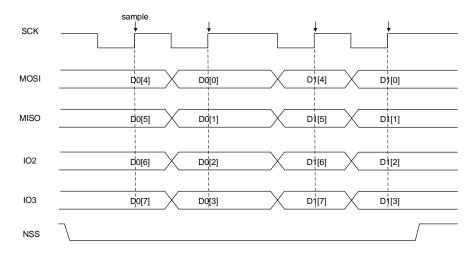

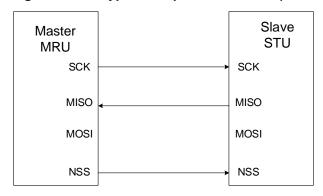

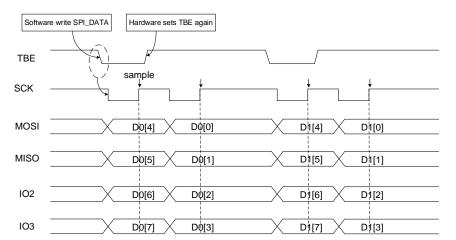

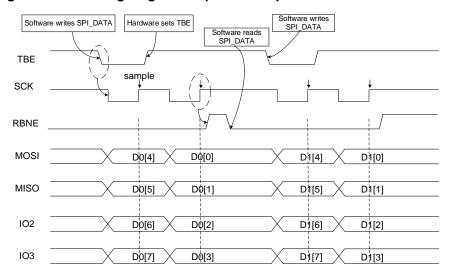

| 21.3.5.      | SPI operating modes                                  | 539 |

| 21.3.6.      | DMA function                                         | 548 |

| 21.3.7.      | CRC function                                         | 548 |

| 21.3.8.      | SPI interrupts                                       | 549 |

| 21.4.        | I2S function overview                                | 550 |

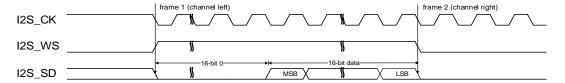

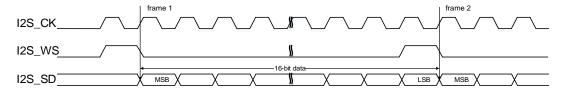

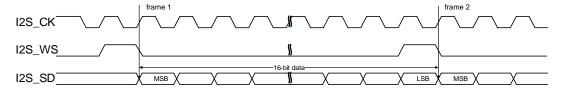

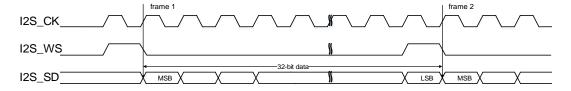

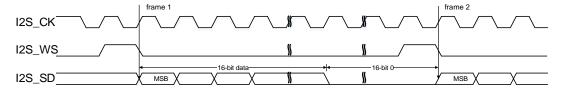

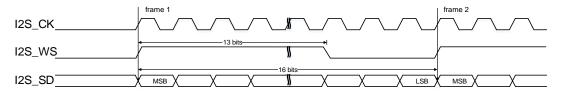

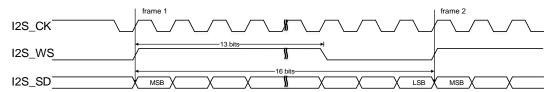

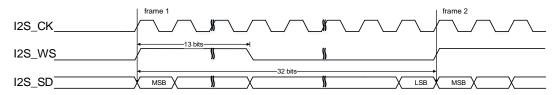

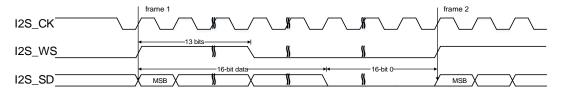

| 21.4.1.      |                                                      |     |

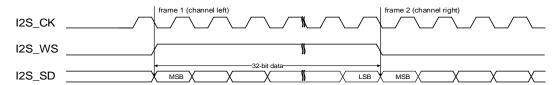

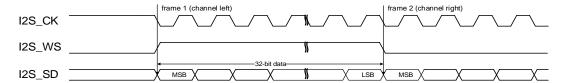

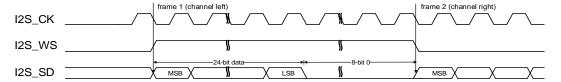

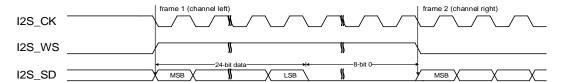

| 21.4.2.      | I2S signal description                               | 551 |

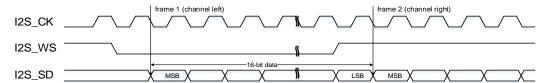

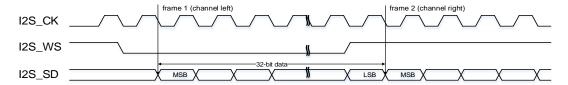

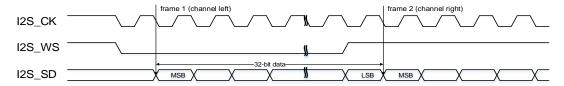

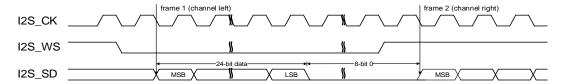

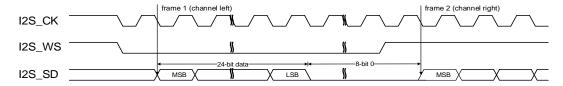

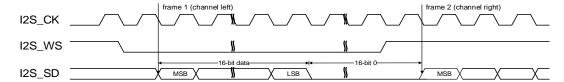

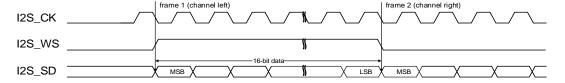

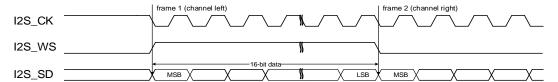

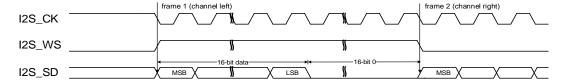

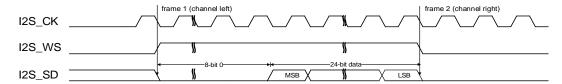

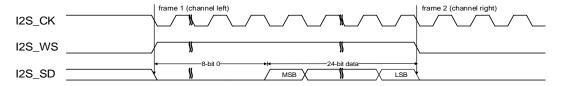

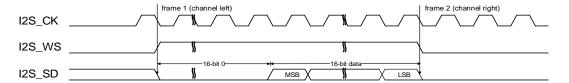

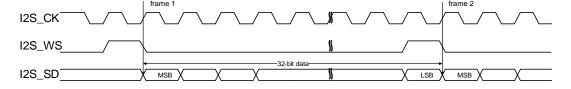

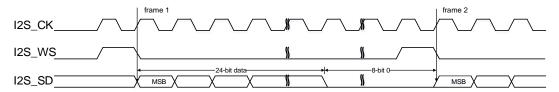

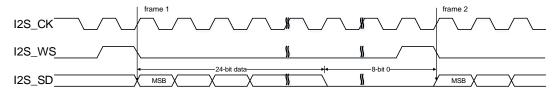

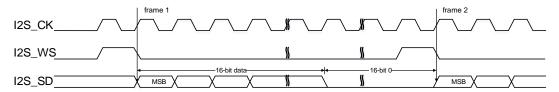

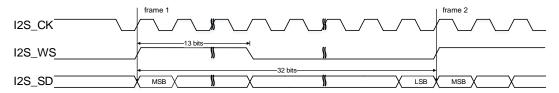

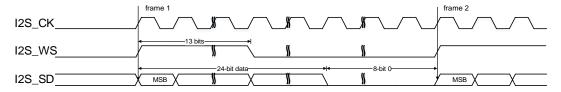

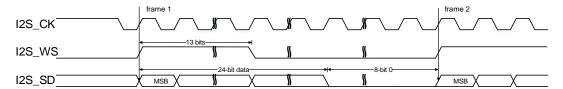

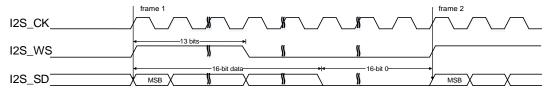

| 21.4.3.      | -                                                    |     |

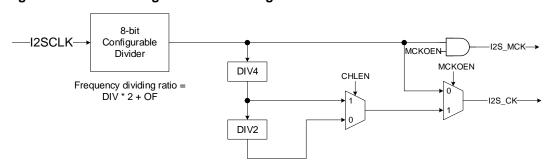

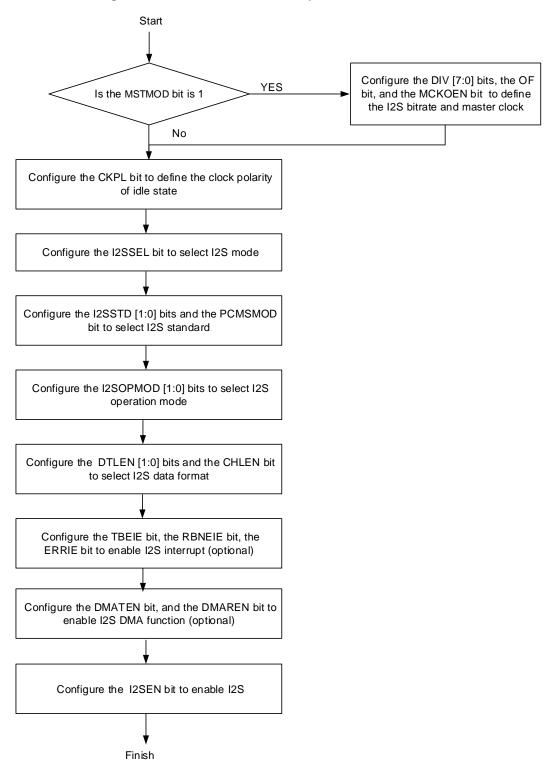

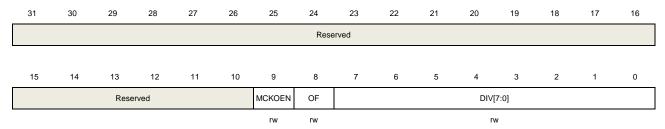

| 21.4.4.      | I2S clock                                            | 559 |

| 21.4.5.      | Operation                                            | 560 |

| 21.4.6.      |                                                      |     |

| 21.4.7.      | I2S interrupts                                       | 564 |

| 21.5.        | Register definition                                  | 566 |

| 21.5.1.      | •                                                    |     |

|              | Control register 1 (SPI_CTL1)                        |     |

| 21.5.3.      |                                                      |     |

| 21.5.4.      | ,                                                    |     |

| 21.5.5.      |                                                      |     |

| 21.5.6.      |                                                      |     |

| 21.5.7.      | · · · · · · · · · · · · · · · · · · ·                |     |

| 21.5.8.      | · · · · /                                            |     |

| 21.5.9.      | - , <u>-</u> ,                                       |     |

|              | D. Quad-SPI mode control register (SPI_QCTL) of SPI0 |     |

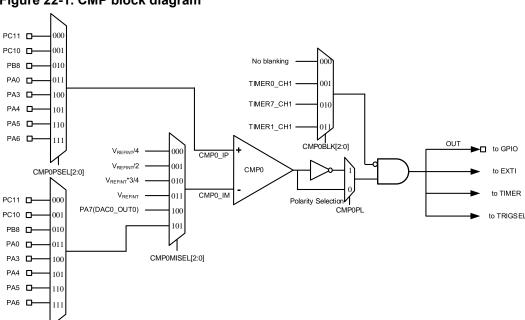

|              | mparator (CMP)                                       |     |

| 22.1.        | Overview                                             |     |

| 22.2.        | Characteristics                                      |     |

|              |                                                      |     |

| <b>22.3.</b> | Function overview                                    |     |

| ZZ.J. I.     | CIVIL GIOGN                                          |     |

# GD32A50x User Manual

| 22.3.2.            | CMP I / O configuration                                                 | 578 |

|--------------------|-------------------------------------------------------------------------|-----|

| 22.3.3.            | CMP operating mode                                                      | 579 |

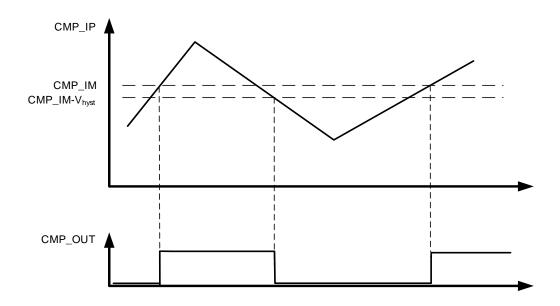

| 22.3.4.            | CMP hysteresis                                                          | 580 |

| 22.3.5.            | CMP register write protection                                           | 580 |

| 22.3.6.            | CMP output blanking                                                     | 580 |

| 22.3.7.            | CMP voltage scaler function                                             | 581 |

| 22.3.8.            | CMP interrupt                                                           | 581 |

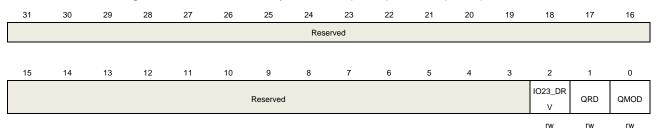

| 22.4.              | Register definition                                                     | 582 |

| 22.4.1.            | •                                                                       |     |

|                    | • · · - ·                                                               |     |

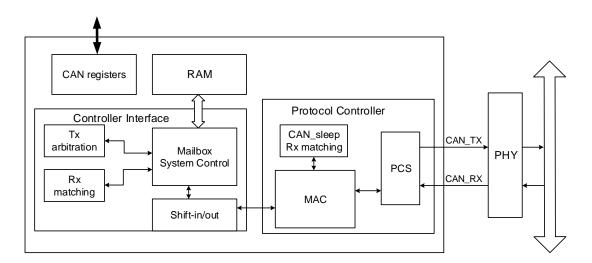

| 23. Cor            | troller area network (CAN)                                              | 585 |

| 23.1.              | Overview                                                                | 585 |

| 23.2.              | Characteristics                                                         | 585 |

| -                  |                                                                         |     |

|                    | Function overview                                                       |     |

| 23.3.1.            | •                                                                       |     |

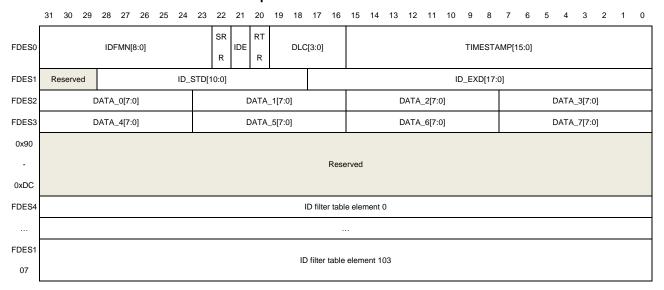

| 23.3.2.            | Rx FIFO descriptor                                                      |     |

| 23.3.3.            | Communication modes                                                     |     |

| 23.3.4.            | Power saving modes                                                      |     |

| 23.3.5.            | Data transmission                                                       |     |

| 23.3.6.<br>23.3.7. | Data reception  Data reception in Pretended Networking mode             |     |

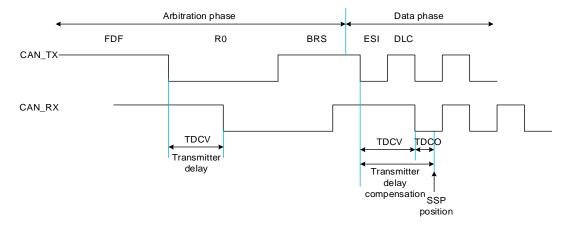

| 23.3.7.            | CAN FD operation                                                        |     |

| 23.3.9.            | ·                                                                       |     |

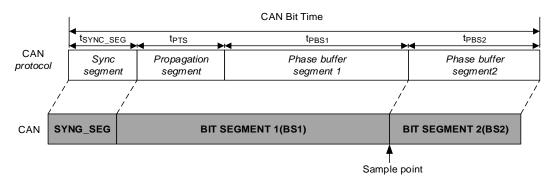

|                    | Communication parameters                                                |     |

|                    | Interrupts                                                              |     |

|                    | •                                                                       |     |

| 23.4.              | Example for a typical configuration flow of CAN                         | 624 |

| 23.5.              | CAN registers                                                           | 627 |

| 23.5.1.            | Control register 0 (CAN_CTL0)                                           | 627 |

| 23.5.2.            | Control register 1 (CAN_CTL1)                                           | 629 |

| 23.5.3.            | Timer register (CAN_TIMER)                                              | 631 |

| 23.5.4.            | Receive mailbox public filter register (CAN_RMPUBF)                     | 631 |

| 23.5.5.            | Error register 0 (CAN_ERR0)                                             | 632 |

| 23.5.6.            | Error register 1 (CAN_ERR1)                                             | 632 |

| 23.5.7.            | Interrupt enable register (CAN_INTEN)                                   | 635 |

| 23.5.8.            | Status register (CAN_STAT)                                              | 636 |

| 23.5.9.            | Control register 2 (CAN_CTL2)                                           |     |

|                    | . CRC for classical frame register (CAN_CRCC)                           |     |

|                    | . Receive FIFO public filter register (CAN_RFIFOPUBF)                   |     |

|                    | Receive FIFO identifier filter matching number register (CAN_RFIFOIFMN) |     |

|                    | Bit timing register (CAN_BT)                                            |     |

|                    | . Receive FIFO/mailbox private filter x register (CAN_RFIFOMPFx)(x=031) |     |

| 23.5.15            | 5. Pretended Networking mode control register 0 (CAN_PN_CTL0)           | 642 |

| 23.5.16. Prete | ended Networking mode timeout register (CAN_PN_TO)                                | 644        |

|----------------|-----------------------------------------------------------------------------------|------------|

| 23.5.17. Prete | ended Networking mode status register (CAN_PN_STAT)                               | 644        |

| 23.5.18. Prete | ended Networking mode expected identifier 0 register (CAN_PN_EID0)                | 645        |

| 23.5.19. Prete | ended Networking mode expected DLC register (CAN_PN_EDLC)                         | 646        |

| 23.5.20. Prete | ended Networking mode expected data low 0 register (CAN_PN_EDL0)                  | 646        |

| 23.5.21. Prete | ended Networking mode expected data low 1 register (CAN_PN_EDL1)                  | 647        |

| 23.5.22. Prete | ended Networking mode identifier filter / expected identifier 1 register          |            |

| (CAN_PN_IFE    | EID1)                                                                             | 648        |

| 23.5.23. Prete | ended Networking mode data 0 filter / expected data high 0 register               |            |

| (CAN_PN_DF     | 0EDH0)                                                                            | 648        |

| 23.5.24. Prete | ended Networking mode data 1 filter / expected data high 1 register               |            |

| (CAN_PN_DF     | 1EDH1)                                                                            | 649        |

| 23.5.25. Prete | ended Networking mode received wakeup mailbox x control status information regist | er         |

| (CAN_PN_RW     | VMxCS)(x=03)                                                                      | 650        |

| 23.5.26. Prete | ended Networking mode received wakeup mailbox x identifier register               |            |

| `              | VMxI)(x=03)                                                                       | 651        |

| 23.5.27. Prete | ended Networking mode received wakeup mailbox x data 0 register                   |            |

| (CAN_PN_RW     | VMxD0)(x=03)                                                                      | 651        |

|                | ended Networking mode received wakeup mailbox x data 1 register                   |            |

| (CAN_PN_RW     | VMxD1)(x=03)                                                                      | 652        |

|                | control register (CAN_FDCTL)                                                      |            |

| 23.5.30. FD b  | oit timing register (CAN_FDBT)                                                    | 653        |

| 23.5.31. CRC   | C for classical and FD frame register (CAN_CRCCFD)                                | 654        |

| 24. Appendix   | <                                                                                 | <b>656</b> |

| • •            | f abbreviations used in register                                                  |            |

|                |                                                                                   |            |

| 24.2. List of  | f terms                                                                           | 656        |

| 24.3. Availa   | able peripherals                                                                  | 657        |

| 25. Revision   | history6                                                                          | 358        |

# **List of Figures**

| Figure 1-1. The structure of the Cortex®-M33 processor          | 26  |

|-----------------------------------------------------------------|-----|

| Figure 1-2. Series system architecture of GD32A50x series       | 28  |

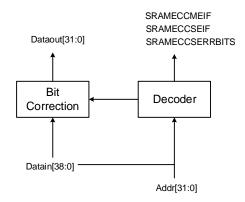

| Figure 1-3. ECC decoder                                         |     |