**GigaDevice Semiconductor Inc.**

# **Device limitations of GD32E51x**

**Errata Sheet**

# **Table of Contents**

| Table                       | of Contents2                                                                                                    |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------|

| List of                     | f Figures3                                                                                                      |

| List of                     | f Tables4                                                                                                       |

| 1. I                        | ntroduction                                                                                                     |

| 1.1.                        | Revision identification5                                                                                        |

| 1.2.                        | Summary of device limitations5                                                                                  |

| 2. C                        | Descriptions of device limitations7                                                                             |

| <b>2.1.</b><br>2.1.<br>2.1. |                                                                                                                 |

| <b>2.2.</b><br>2.2.         |                                                                                                                 |

| <b>2.3.</b><br>2.3.         | <ul> <li>DAC</li></ul>                                                                                          |

| <b>2.4.</b><br>2.4.<br>2.4. | - 5                                                                                                             |

| <b>2.5.</b><br>2.5.         | <b>EXMC</b> 9         1. NE timing can not satisfy the requirement when using NAND pre-waiting function       9 |

| <b>2.6</b> .<br>2.6.        | <ul> <li>USB</li></ul>                                                                                          |

| 3. F                        | Revision history                                                                                                |

# **List of Figures**

| Figure 1-1. Device revision code of GD32E51x5 |

|-----------------------------------------------|

|-----------------------------------------------|

# **List of Tables**

| Table 1-1. Applicable products | . 5 |

|--------------------------------|-----|

| Table 1-2. Device limitations  | . 5 |

| Table 3-1. Revision history    | .11 |

# 1. Introduction

This document applies to GD32E51x product series, as shown in <u>Table 1-1. Applicable</u> <u>products</u>. It provides the technical details that need to be paid attention to in the process of using GD32 MCU, as well as solutions to related problems.

| Туре | Part Numbers       |

|------|--------------------|

|      | GD32E513xx series  |

| MCU  | GD32E517xx series  |

| MCO  | GD32E518xx series  |

|      | GD32EPRTxxA series |

## 1.1. Revision identification

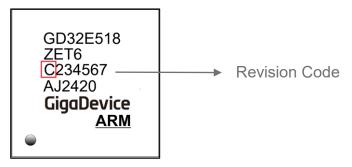

The device revision can be determined by the mark on the top of the package. The 1st code on the line 3 of the mark represents product revision code. As the picture shown in <u>Figure</u> <u>1-1. Device revision code of GD32E51x</u>.

Figure 1-1. Device revision code of GD32E51x

## 1.2. Summary of device limitations

The device limitations of GD32E51x are shown in <u>*Table 1-2. Device limitations*</u>, please refer to section 2 for more details.

| Module | Limitations                                                                         | Workaround  |

|--------|-------------------------------------------------------------------------------------|-------------|

| wodule |                                                                                     | Rev. Code C |

| RCU    | MCU cannot be waked up from Deepsleep mode when DSLP_HOLD bit is set                | Y           |

| RCU    | The LXTALSTB bit cannot be cleared by disabling LXTAL when LXTAL stops unexpectedly | Y           |

| ADC    | ADC data acquisition error occurs when the ADC clock is much                        | Y           |

Table 1-2. Device limitations

# Device limitations of GD32E51x

| Module | Limitations                                                                                                                                           | Workaround  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| wodule |                                                                                                                                                       | Rev. Code C |

|        | slower than the PCLK clock                                                                                                                            |             |

| DAC    | In the DAC noise mode, when the value (DH+DWBW) is configured more than 4095, the DAC output voltage will have an abnormal break point                | Y           |

|        | Read one more data because the BTC flag was not cleared                                                                                               | Y           |

| I2C    | When SDA line interference causes garbled data on the I2C bus,<br>it can lead to a stuck in the I2C2 slave device                                     | Ν           |

| EXMC   | NE timing can not satisfy the requirement when using NAND pre-<br>waiting function                                                                    | Y           |

| USB    | When USBHS device uses an internal PHY and is suspended by<br>the host, its suspension interrupt flag and wakeup interrupt flag<br>are frequently set | N           |

#### Note:

Y = Limitation present, workaround available

N = Limitation present, no workaround available

'--' = Limitation fixed

# 2. Descriptions of device limitations

## 2.1. RCU

#### 2.1.1. MCU cannot be waked up from Deepsleep mode when DSLP\_HOLD bit

#### is set

#### **Description & impact**

When the DSLP\_HOLD bit in the DBG\_CTL register is set, the MCU cannot be waked up after the MCU enters deepsleep mode.

#### Workarounds

When the DSLP\_HOLD bit is set to enable low power debugging, the application programme need switch the system clock to IRC8M before entering the deepsleep mode.

#### 2.1.2. The LXTALSTB bit cannot be cleared by disabling LXTAL when LXTAL

#### stops unexpectedly

#### **Description & impact**

When LXTAL stops unexpectedly, the LXTALSTB bit cannot be cleared by disabling the LXTAL, which prevents the LXTAL from restarting.

#### Workarounds

By repeatedly setting and resetting the LXTALBPS more than ten times to clear the LXTALSTB bit, and then reconfiguring the LXTAL. The reference code for clearing LXTALSTB bits is as follows:

```

void Ixtal_stb_clear(void)

{

volatile uint32_t i = 0U;

/* close LXTAL clock */

rcu_osci_off(RCU_LXTAL);

for(i = 0; i < 10; i++) {

/* enable the LXTAL bypass mode */

rcu_osci_bypass_mode_enable(RCU_LXTAL);

/* disable the LXTAL bypass mode */

rcu_osci_bypass_mode_disable(RCU_LXTAL);

}

}</pre>

```

## 2.2. ADC

#### 2.2.1. ADC data acquisition error occurs when the ADC clock is much slower

#### than the PCLK clock

#### **Description & impact**

When the ADC clock is much slower than the PCLK clock, the ADC\_RDATA register is read immediately after the EOC is set and a data acquisition error occurs.

#### Workarounds

When the delay between reading EOC flag and reading ADC\_RDATA is no more than two ADC clocks, after the EOC flag is set, software need to delay two ADC clocks before reading the ADC\_RDATA register.

### 2.3. DAC

#### 2.3.1. In the DAC noise mode, when the value (DH+DWBW) is configured more

#### than 4095, the DAC output voltage will have an abnormal break point

#### **Description & impact**

When the DAC is configured in noise mode and the DAC output value is set to a large value, the superimposed value (DH+DWBW) will exceed the maximum value of 4095, resulting in an abnormal break point of zero voltage in the DAC output signal.

#### Workarounds

When the DAC output value and the noise wave peak value are configured, avoid the superimposed value (DH+DWBW) overflow.

### 2.4. I2C

#### 2.4.1. Read one more data because the BTC flag was not cleared

#### **Description & impact**

If an interrupt occurs before reading I2C\_DATA register when RBNE flag is set and BTC flag is reset, I2C will read an additional data if BTC flag is set during the interrupt processing because the read data operation cannot clear the BTC flag.

#### Workarounds

Use one of the following solutions:

- 1) Using interrupt method to read the I2C\_DATA register (need higher interrupt priority).

- 2) Using DMA method to read the I2C\_DATA register (recommend).

#### 2.4.2. When SDA line interference causes garbled data on the I2C bus, it can

#### lead to a stuck in the I2C2 slave device

#### **Description & impact**

When I2C2 operates as a slave and is configured in 10-bit addressing mode, and if there is a mismatch in the 10-bit address header or the lower 8 bits of the 10-bit address during the I2C2 slave addressing phase, interference on the SCL / SDA line that causes the next RESTART / STOP signal to be sent early can result in the I2C2 slave pulling the SDA line low, ultimately leading to the I2C2 slave stuck.

Note: This limitation applies to I2C2.

#### Workarounds

Not available.

### 2.5. EXMC

#### 2.5.1. NE timing can not satisfy the requirement when using NAND pre-waiting

#### function

#### **Description & impact**

For some EXMC\_NCE-sensitive NAND Flash, NE timing can not satisfy the requirement when using NAND pre-waiting function. NE signal keeps the low level when EXMC\_INTx is active.

#### Workarounds

Using general I/O port to simulate the NE timing to finish the NAND reading and writing, NE signal keeps the low level after starting reading or writing.

### 2.6. USB

#### 2.6.1. When USBHS device uses an internal PHY and is suspended by the host,

#### its suspension interrupt flag and wakeup interrupt flag are frequently set

**Description & impact**

When a USBHS device uses an internal PHY and is suspended by the host, its suspension interrupt flag (SP) and wakeup interrupt flag (WKUPIF) are frequently set.

#### Workarounds

Not available. But it does not affect the normal use of USBHS.

# 3. Revision history

#### Table 3-1. Revision history

| Revision No. | Description     | Date         |

|--------------|-----------------|--------------|

| 1.0          | Initial Release | Aug.22, 2024 |

#### Important Notice

This document is the property of GigaDevice Semiconductor Inc. and its subsidiaries (the "Company"). This document, including any product of the Company described in this document (the "Product"), is owned by the Company under the intellectual property laws and treaties of the People's Republic of China and other jurisdictions worldwide. The Company reserves all rights under such laws and treaties and does not grant any license under its patents, copyrights, trademarks, or other intellectual property rights. The names and brands of third party referred thereto (if any) are the property of their respective owner and referred to for identification purposes only.

The Company makes no warranty of any kind, express or implied, with regard to this document or any Product, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. The Company does not assume any liability arising out of the application or use of any Product described in this document. Any information provided in this document is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Except for customized products which has been expressly identified in the applicable agreement, the Products are designed, developed, and/or manufactured for ordinary business, industrial, personal, and/or household applications only. The Products are not designed, intended, or authorized for use as components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, atomic energy control instruments, combustion control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or Product could cause personal injury, death, property or environmental damage ("Unintended Uses"). Customers shall take any and all actions to ensure using and selling the Products in accordance with the applicable laws and regulations. The Company is not liable, in whole or in part, and customers shall and hereby do release the Company as well as it's suppliers and/or distributors from any claim, damage, or other liability arising from or related to all Unintended Uses of the Products. Customers shall indemnify and hold the Company as well as it's suppliers and/or distributors harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of the Products.

Information in this document is provided solely in connection with the Products. The Company reserves the right to make changes, corrections, modifications or improvements to this document and Products and services described herein at any time, without notice.

© 2024 GigaDevice - All rights reserved